El futuro de cualquier procesador actual está en tela de juicio. Estamos llegando a ciertos límites que están forzando la pericia de los ingenieros de arquitecturas de transistores para lograr un avance escalable de cara a los próximos años en cualquier tipo de chip. Solemos hablar de Intel, TSMC o Samsung y sus evoluciones, pero IBM y CEA-Leti también tienen mucho que decir, ya que, aunque han tomado caminos diferentes, su concepción de los nuevos transistores es interesante y se basará en dos conceptos distintos: AS-Late y GAA 7 Layer.

IBM siempre ha tenido fama de ser una empresa tecnológica líder en la industria y aunque muchas veces se la pone tras Intel, lo cierto es que en no pocos campos está mucho más avanzada que esta. En transistores, pieza fundamental de cualquier chip en el mundo, su equipo IBM Research presentó un nuevo trabajo sobre nanohojas llamado AS-Late.

Bolsas de aire alrededor de una Gate (AS-Late), ¿el paso definitivo para ralentizar los nm?

Lo descubierto por IBM fue trabajado en base a una especialización de la tecnología nanosheet, donde descubrieron que creando una especie de bolsa alrededor de las gates cada transistor consumía menos potencia y lograba un mejor desempeño, lo que se traducía en mayor rendimiento final.

A esto la compañía lo llamó espaciadores de aire, porque realmente esa es su función, añadir un espacio físico, donde lo mejor es que es universal para cualquier arquitectura de transistores, con la consecuente repercusión que ello conlleva. El hallazgo es de tal calibre, que IBM mostró que es mejor aplicar esta técnica que reducir su nodo de 7 nm a 5 nm, ya que se conseguía ganar rendimiento y consumir menos energía por transistor, por lo que ya podemos hacernos una idea de la importancia que podría tener esto en la industria.

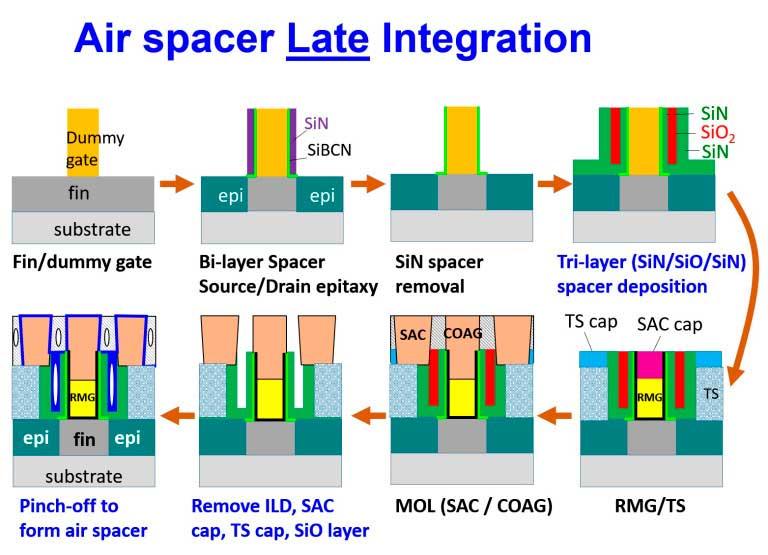

El secreto está en la reducción de la capacitancia efectiva, un proceso que disminuye el rendimiento del transistor desde el punto de vista de la eficiencia y que con los espaciadores de aire se logra reducir en un 15%. El proceso para llegar a esto es bastante sencillo desde el punto de vista conceptual, pero muy complicado de realizar a nivel atómico.

El espaciador es un aislamiento físico entre la gate y los contactos de cada transistor, de manera que dicho espacio funciona como un switch. Cuando la puerta se abre para favorecer el paso de corriente la electricidad fluye y el espaciador asegura que sea la propia puerta la que controle el flujo, mientras que mantiene aisladas las demás partes adyacentes del mismo.

Debido a su funcionamiento la técnica ha tomado por nombre air spacer early (AS-Early) y tiene una versión todavía más avanzada llamada AS-Late, donde la formación del espaciador se realiza no al principio de la creación del transistor, sino al final, por lo que según dice IBM es más escalable.

GAA 7 Layer, la apuesta de CEA-Leti para las nanosheets

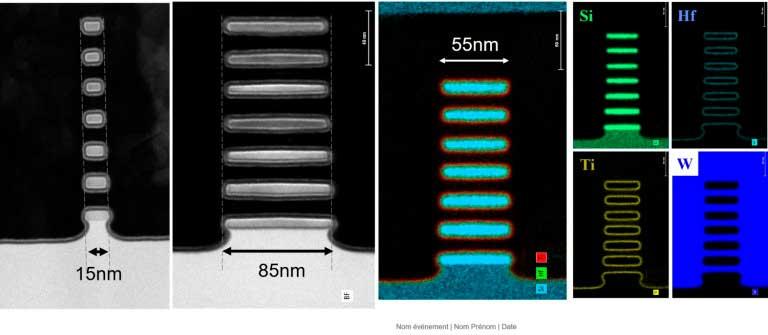

La compañía al contrario que IBM ve como Intel y TSMC el mercado de los transistores. Para ellos FinFET es el pasado y ahora llega un nuevo futuro con GAA. En su desarrollo de esta tecnología por capas o también llamadas hojas, sus ingenieros lograron crear transistores con siete niveles de silicio apilados verticalmente.

Esto ya de por sí es digno de mención puesto que supone aumentar al doble el número de sheets por transistor, pero lo más increíble son los anchos conseguidos, ya que van desde los 15 nm hasta los 85 nm.

Lo que buscaba CEA-Leti es mejorar la capacidad de conducción de corriente y el drenaje por transistor. Así, afirman haber conseguido cifras de 3 mA / μm a VDD = 1V y un drenaje tres veces superior a lo actual. Esto es posible por el aumento del número de canales apilados.

Un mayor número implica una mayor corriente de excitación y con ello es posible un desempeño mucho más efectivo, hasta el punto de que actualmente están a la vanguardia en este campo, muy por delante de Samsung e Intel. El futuro según la compañía para por modular este hecho, de manera que dependiendo del rendimiento que quiera conseguirse se puede cambiar el ancho de las nanosheet, permitiendo diseños más flexibles, algo que en FinFET es imposible.

Como vemos, todos aprietan por uno u otro bando. Quizás TSMC haya encontrado una solución similar a AS-Late y por ello siga en FinFET hasta los 3 nm, quien sabe. En cualquier caso, en no más de tres años estaremos con GAA en el mercado, porque en esto sí hay unanimidad en el sector: FinFET está muerto, larga vida a GAA.