AMD Zen 4 podría usar los 5 nm de TSMC: un 80% más de densidad y mejora del 15% en rendimiento

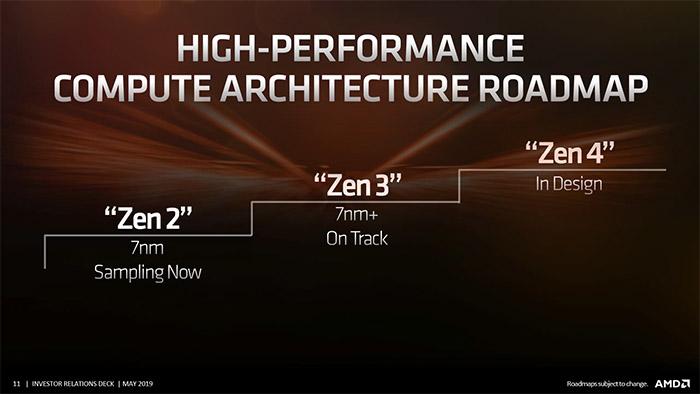

No ha sido presentado Zen 2 y ya tenemos los primeros rumores de una arquitectura que actualmente se encuentra en diseño por parte de AMD. Pero es que los movimientos y declaraciones del CEO de TSMC han provocado un revuelo bastante interesante, ya que en su afán de posicionar a su compañía como la más puntera del mundo dejó caer ciertas declaraciones interesantes. ¿Zen 4 usará finalmente sus 5 nm?

Los 5 nm están en pruebas, aunque los 6 nm parecen estar más cerca

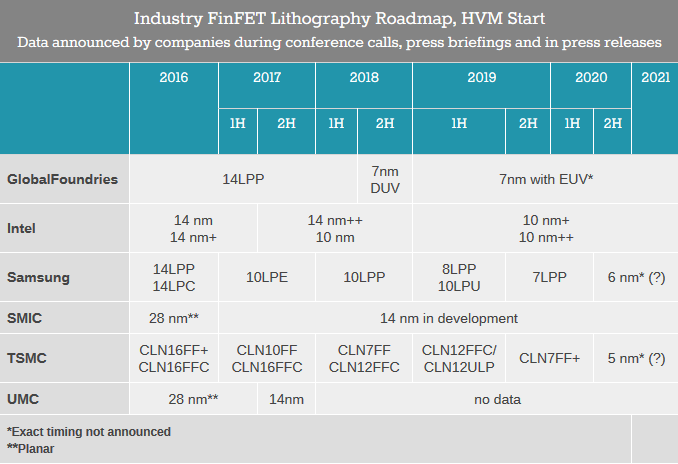

Si nos sigues diariamente, ya estarás al tanto de todo lo que está moviendo TSMC, como mantiene el pulso a un gigante como Samsung y como está poniendo en jaque a Intel. Aunque en estos casos y por norma general, una compañía dice hoy blanco y mañana puede decir gris o negro, ya que 2+2 aquí no son 4 y menos en tiempos de entrega, lo cierto es que TSMC parece estar cumpliendo con lo que dijo anteriormente.

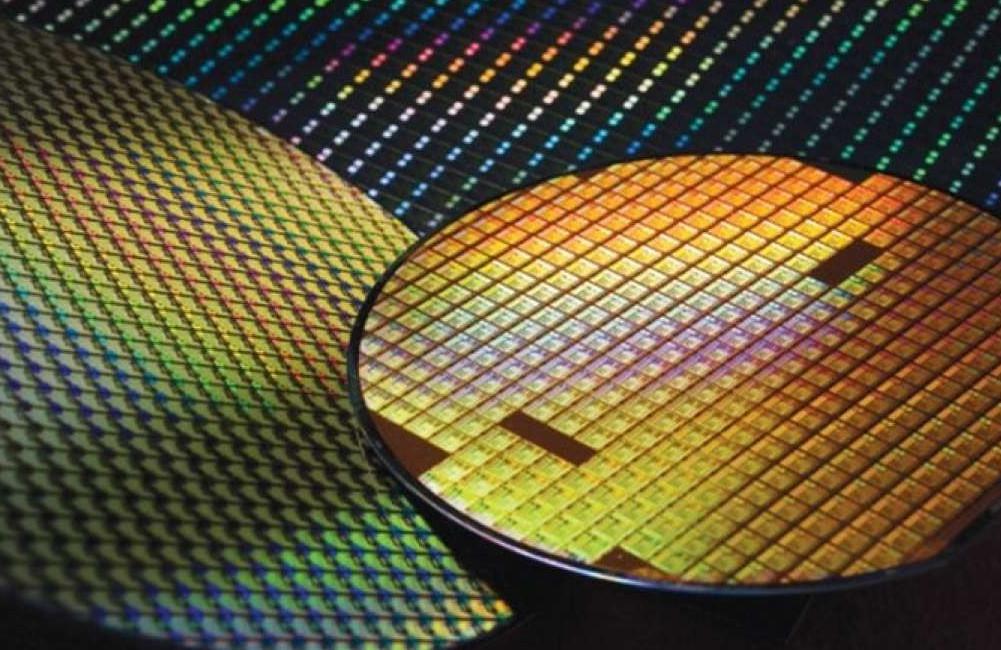

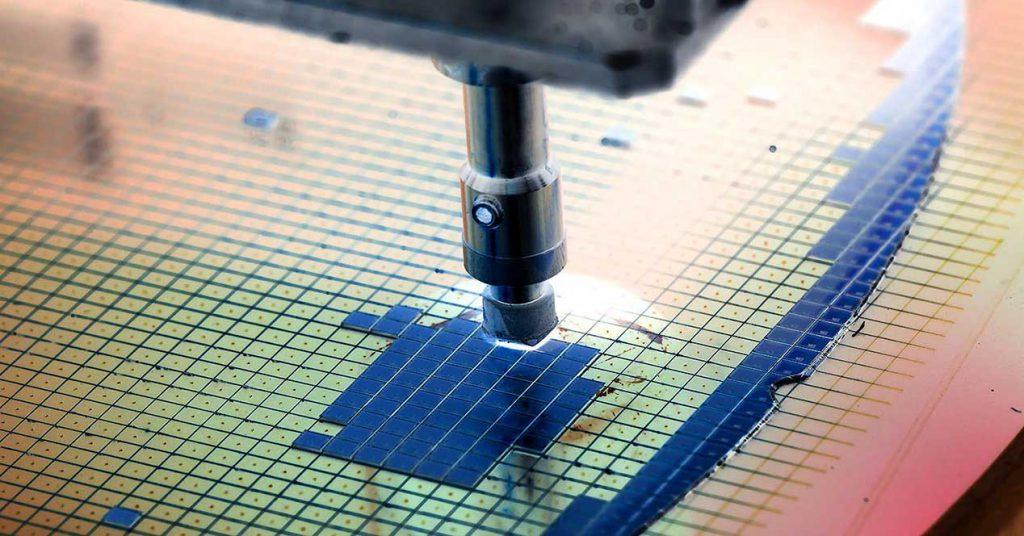

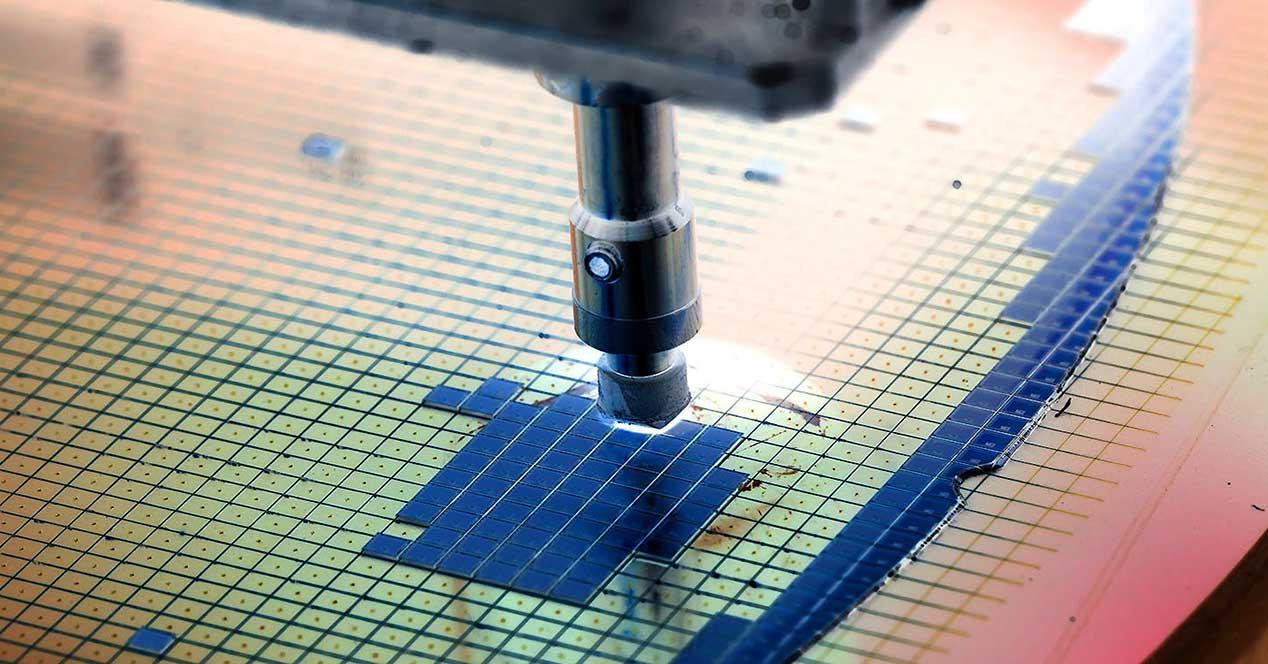

Aunque es cierto que actualmente el rendimiento por oblea se sitúa en márgenes irrisorios para chips complejos, el proceso sigue su curso mediante los primeros Process Design Kits para desarrolladores. Esto quiere decir que el potencial del proceso litográfico está cerca de ser conseguido, donde en un principio los chips creados serán más simples y a medida que se depure se irá acrecentando la brecha hacia el alto rendimiento.

Dicho proceso litográfico y según el roadmap de TSMC estará listo para 2021, lo cual indica (de no sufrir retrasos) que sería el nodo disponible para AMD en el momento de tener que lanzar Zen 4 y de ahí todas las especulaciones que veremos a continuación.

Mucho más denso, mucho más rápido, pero mucho más difícil de fabricar

Las mejoras que tiene previstas TSMC para sus socios (entre ellos AMD, lógicamente) son realmente espectaculares. No hablamos de un salto cualquiera, sino de un salto (seguramente el primero) de un patrón simple a un patrón doble. De esto ya hablamos ayer en nuestro artículo de cómo afectará EUV a Intel y AMD, y al que os remitimos para comprender todo esto.

Dicho salto al posible uso del doble patrón implica un importante salto de la densidad y del rendimiento, siendo estos de aproximadamente un 80% de mejora en la inclusión de transistores/capas/conexiones y un 15% de impulso en el rendimiento, siempre teniendo en mente los 7 nm actuales por inmersión.

Todo esto es realmente importante de cara al usuario final, ya que Intel llegará con retraso (una vez más) a 2021 con sus 7 nm EUV. Y es que estamos a poco más de año y medio para llegar a dicha cifra, donde sus 10 nm entrarán en producción masiva en 2020, cuando AMD ya esté en el mercado consolidada con sus 7 nm y Zen 2.

Además, ya tendrá listos sus Zen 3 a 7 nm+ y visto lo visto, muy bien encarados los 5 nm para Zen 4.

Existen rumores sobre los 6 nm, sí, pero realmente y según lo que adelantó el CEO de TSMC, los plazos para que esté listo en obleas de 12 pulgadas y en alto rendimiento no cuadrarían en un principio con el roadmap de AMD para CPUs, pero sí quizás para Navi 20, como ya vimos en otro artículo.

El problema de todo esto es que actualmente TSMC tiene dos líneas de trabajo distintas enfocadas a los distintos patrones en EUV. Esto viene dado por intentar ofrecer obleas con procesos litográficos atractivos para sus clientes, ya que al parecer Samsung está consiguiendo mejorar en este aspecto y podría ofrecer precios más competitivos.