Aunque todavía está un poco lejos, TSMC se encargará una vez más de dar vida a los chips de AMD para la novedosa arquitectura Zen 4 bajo su nodo de 5 nm, también llamado N5. Aunque por parte de AMD no sabemos nada de Zen 4, sí podemos adelantar casi todas las novedades que incluirá este nuevo proceso litográfico, ¿qué ha cambiado con respecto a los 7 nm actuales? ¿cuáles son esas mejoras?

Hay varios factores a tener en cuenta que deben ser desgranados en profundidad, en concreto:

- Será un nodo de alto rendimiento.

- La producción de alto volumen llegará en 2T de este 2020.

- Tendrá una versión de mayor rendimiento un año después, N5P con un +7% de frecuencia o un 15% de reducción del consumo a misma frecuencia.

- Densidad aumentada a 1,8X, SRAM 0,75 y analógica 0,85 frente a 7 nm.

- Consumo entre un 15 y un 30% inferior a misma velocidad frente a 7 nm.

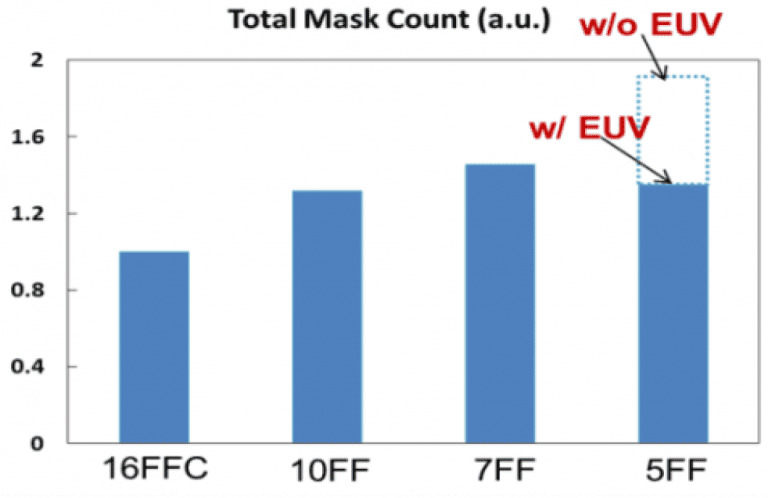

- Solo se usará EUV.

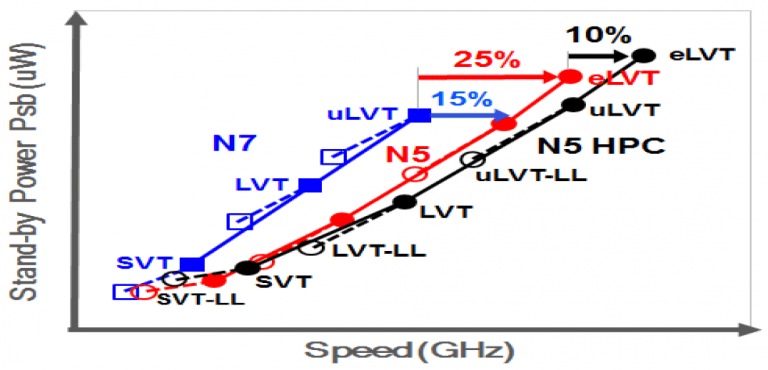

- Transistor E/S de 1,5v o 1,2V y dispositivo LVT extremo un 25% más rápido que el actual de 7 nm.

- Nuevos materiales Low-K.

- Capa de grafeno para reducir la resistividad de la interconexión con el cobre.

Como vemos, las mejoras son notables, pero entremos en algunas de ellas con más profundidad.

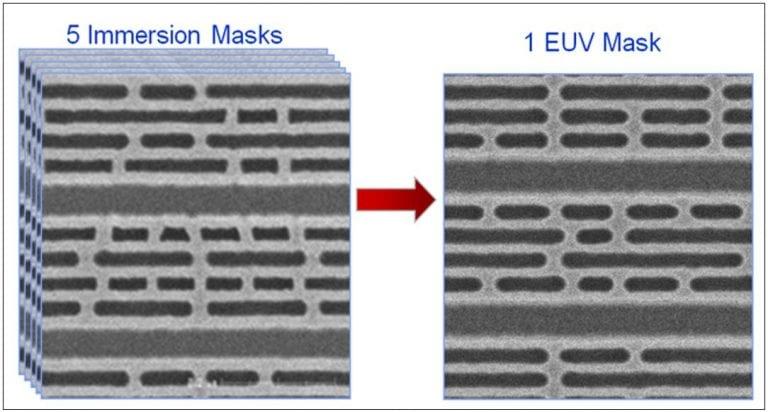

Uso exclusivo de EUV, se acabaron las máscaras de inmersión en 5 nm

Los 5 nm de TSMC son el verdadero sucesor de los 7 nm EUV de la compañía y aunque pueda parecer obvio, entre ellos hay al menos 3 modificaciones o procesos litográficos distintos.

Este nodo necesitará SAQP o LE3 para poder trabajar con las máscaras EUV, donde al usar MxP a 30 nm como calibración de las máscaras obtendrá una altura máxima de 175 nm, lo que es aproximadamente un factor de 0,73 frente a los 7nm actuales.

Esto implica varias mejoras, donde al microscopio se puede ver perfectamente que el patrón resultante es bastante más nítido (imagen superior).

Esto deriva en otro aspecto a tener en cuenta, ya que el número de capas a usar se reduce considerablemente. Por lo tanto, será un proceso puro fabricado en EUV, si necesidad ninguna de inmersión, lo cual favorece la retirada del número total de máscaras, simplificando su diseño.

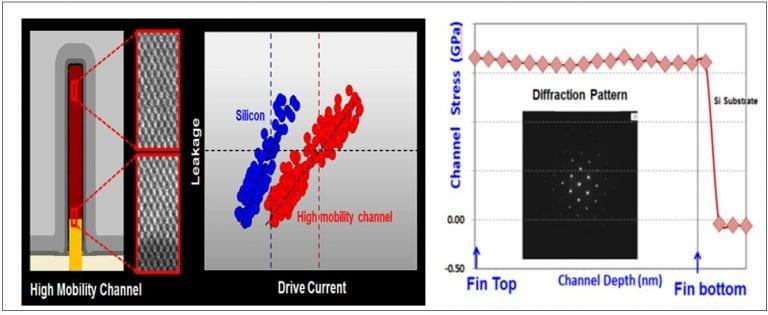

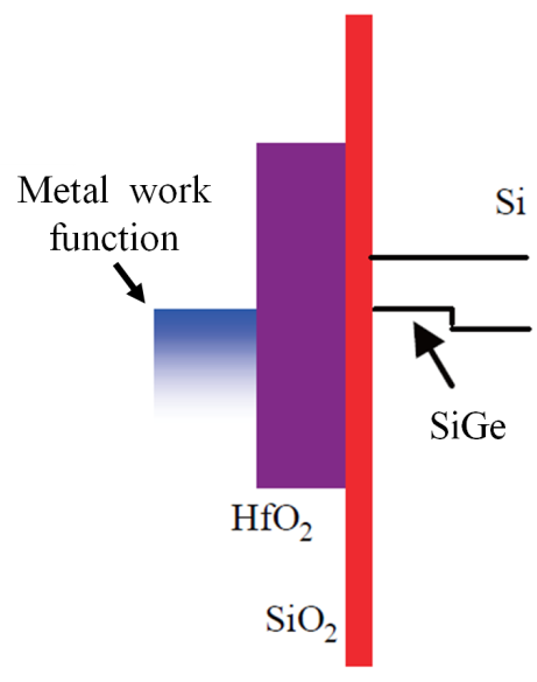

Drive Current mejorado con germanio

La Drive Current o también conocida como corriente de accionamiento de las aletas ha sido mejorada en un 18% gracias a un compuesto basado en el germanio, el cual se ha mezclado con el silicio.

Esto influye en la altura de las aletas del transistor, lo cual añade complejidad al diseño, algo que TSMC no ha aclarado más allá de evidenciar un paso adelante en este apartado.

Se especula incluso con un grabado de las aletas en EUV, lo que sería totalmente revolucionario.

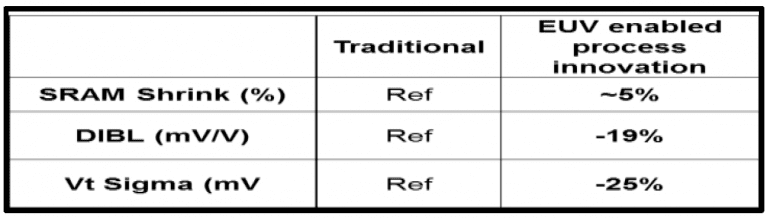

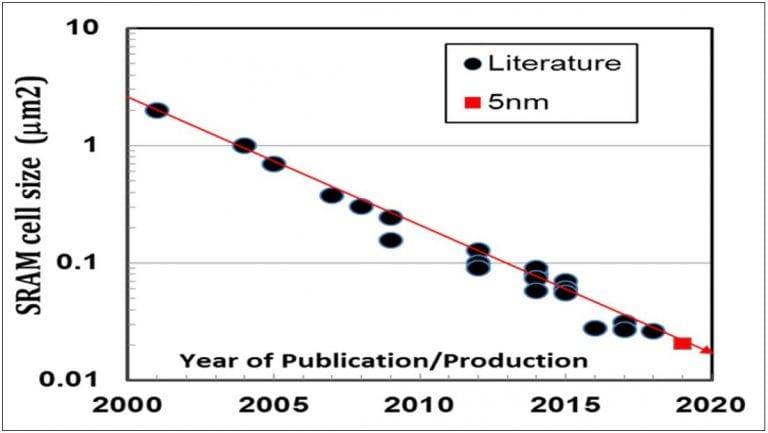

Independientemente de esto, el tamaño de las células de SRAM será el más bajo creado hasta la fecha, con solo 0,021 µm2, por debajo de lo que ofrecerán Intel y Samsung en sus procesos rivales.

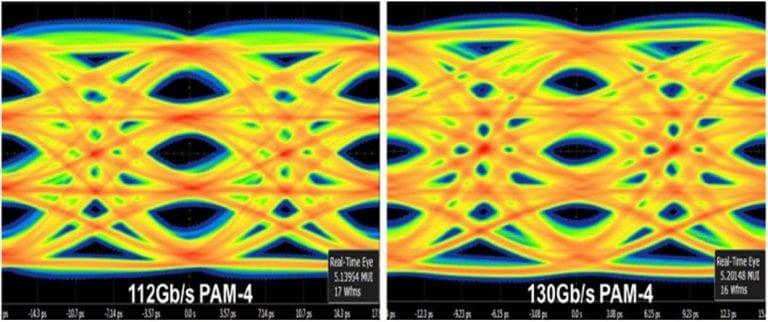

Gracias a esto, el PAM4 SerDes podrá alcanzar una velocidad teórica de 130 Gb/s, habiéndose demostrado hasta ahora que sería capaz de alcanzar 112 Gb/s reales para este nodo de 5 nm.

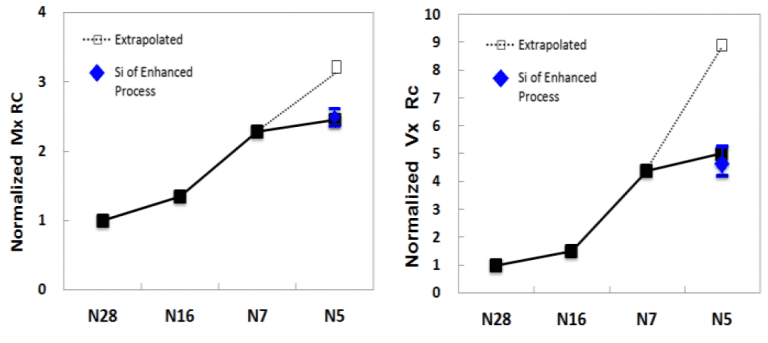

Hasta un 40% de reducción del tamaño del chip

Las mejoras no terminan aquí, ya que las características de este nodo en DTCO (Design-Technology Co-Optimization) han logrado unas nuevas escalas inteligentes en el diseño, el cual se basará en el realizado para los SoC móviles con un 60% de Logic, un 30% de SRAM y un 10% en I/O analógicos.

El resultado es que el tamaño físico del chip puede verse reducido entre un 30 y un 40%. La velocidad será otro punto culmen para este nodo. TSMC asegura un aumento de la velocidad máxima de un +25% frente a los 7 nm, donde además si logran incluir aletas estándar de 3 celdas se lograría otro 10% adiciona para HPC.

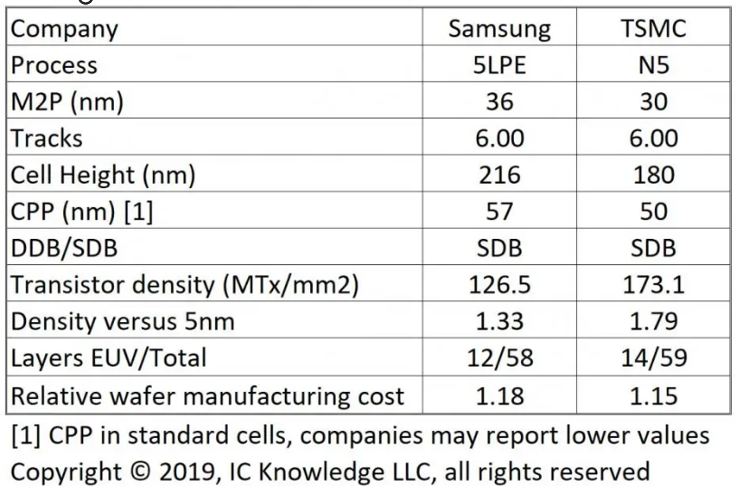

En resumen, TSMC volvería a tener la delantera como mejor nodo del mundo, al menos por delante de Samsung, ya que Intel no ha especificado que podremos ver con sus 7 nm EUV, un proceso litográfico que despierta mucha expectación.

Además, las mejoras en estos 5 nm de TSMC lo posicionan frente a su rival coreano como un coste relativo por oblea algo inferior, por lo que no solo sería más denso, sino más barato para sus clientes.