La industria de los semiconductores la mueven actualmente y en exclusiva tres empresas: Intel, Samsung y TSMC. La lucha está centrada en ellos tres y en el futuro no hay vistas de un nuevo competidor, por lo que quien avance más rápido se llevará el gato al agua. ¿Qué podemos esperar a partir de este año? ¿quién dominará el mercado y arrastrará al mayor número de fabricantes bajo su falda? Hagamos un repaso al organigrama y planificación de los procesos litográficos de los tres grandes.

Como ya hemos visto en otros artículos sobre esta temática, la industria se enfrenta a varios retos a corto y largo plazo para seguir reduciendo de tamaño los transistores de manera que puedan caber cada vez más en el mismo espacio (lo que se llama aumentar la densidad). El primero de ellos es sin duda la bajada de nanómetros para obtener mayor densidad, mayores frecuencias y menores o iguales consumos, pero tras esto hay otras que tienen igual o mayor importancia si cabe.

La transición de los transistores, el primer paso para una nueva era

El principal problema que se encuentra la industria a este respecto es que hay un límite físico que es imposible sobrepasar, por lo que tienen que buscar formas alternativas de seguir aumentando la densidad de los transistores… y ésta puede pasar por dejar de usarlos.

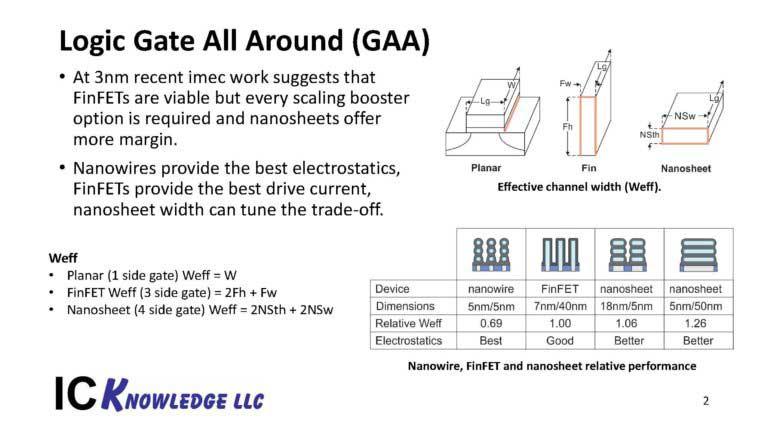

Algo de lo que ya hablamos y que es clave para comprender este artículo, así que no nos extenderemos demasiado aquí. La era de los FinFET llega a su fin, debido principalmente al modo en el que están construidos con sus tres gates por tres lados del transistor. Por mucho que sean transistores 3D, la reducción de nanómetros y con ello del espacio que puede haber entre ellos obliga a la industria a abandonarlos para poder llegar a densidades mayores.

Su sustituto ya tiene nombre y está en fase de producción: Gate All Around o GAA, también conocido como HNS por la implementación de las nanohojas horizontales que integra, principal novedad en este tipo de transistor.

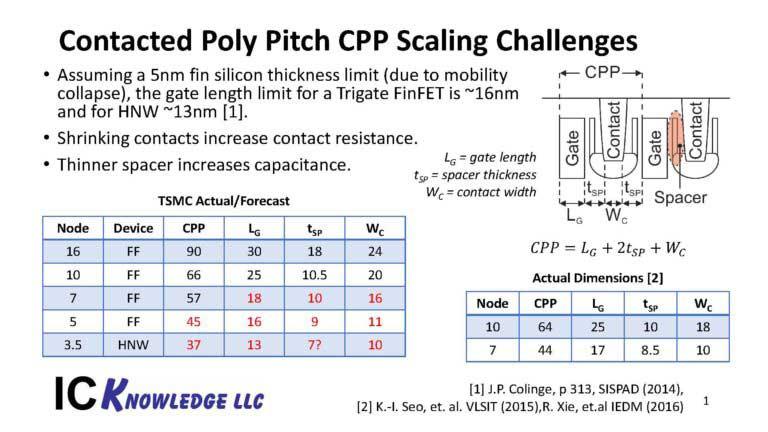

En esta nueva versión las nanocapas son muy estrechas, mejoran los nanocables y la electrostática, por lo que la longitud de las gates se reduce de 16 nm en FinFET a 13 nm (o menos) en GAA, lo cual es directamente dependiente de los Contacted Poly Pitch (CPP), es decir, menor CPP es igual a mayor densidad por pura lógica.

Siendo breves, el problema aquí es que las tres grandes compañías están enfocando esto en distintos tiempos: TSMC no lo implementará hasta, al menos, sus 3 nm, Samsung lo tendrá en producción en 5 nm e Intel no ha dado información al respecto.

Reducción de los fins por cada transistor para ahorrar espacio

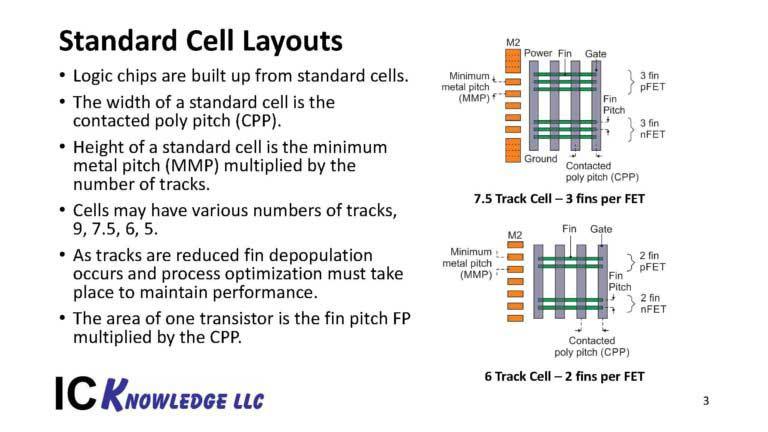

El apilamiento de las hojas y con ello de las gates tendrá otro impacto directo a medida que se sigan reduciendo los nanómetros y no es otro que la reducción de los fins o aletas. Esto tiene implicaciones directas en el control de la corriente de transmisión de un transistor, ya que se les deja menos espacio y opciones a los ingenieros para lograr corrientes constantes y con ello minimizar las fugas.

Todo esto se centra en las celdas, las cuales son parte fundamental para comprender como funcionarán los GAA. Dichas celdas se basan en tracks (pistas), las cuales se van reduciendo a cada salto litográfico para mejorar densidad y con ellas el minimum metal pitch (MMP).

Menor número de celdas reduce tanto el espacio vertical como el horizontal, y debido a esto todos los componentes que forman también tienen que ser reducidos, lo que dificulta la implementación de los transistores.

Por ello, el siguiente paso a GAA (HNS) es el llamado CFET o Complementary FET. Es básicamente un paso más allá en cuanto a la escalabilidad de la densidad, ya que se dota de dos tipos de FET apilados de forma vertical: nFET y pFET.

La diferencia con las Nanohojas en GAA es que se ofrecen dos alturas distintas que a medida que se reducen las celdas pueden añadirse más CFET para compensar, donde las Gate ahora son verticales y con ello se puede reducir más y más el Fin Pitch entre cada CFET.

Lógicamente esto tiene implicaciones de estabilidad todavía por estudiar, pero ya están en proceso por las tres grandes. No sabemos cuál será finalmente la implementación de cada una ni cómo piensan solventar problemas como las interconexiones (artículo exclusivo de este tema en breve), pero las mejoras primigenias son de tal calibre que estamos seguros de que es el camino a seguir (desde 1,4X hasta 2X en los mejores diseños).

Perspectivas de los procesos litográficos en 2020, 2021 y 2022

Aunque parezca que la industria tiene planes de futuro a largo plazo, la realidad es que van bastante justos en cuanto al tiempo se refiere. Por ello y viendo todo lo anterior y los artículos que están por venir, tenemos que pensar que el futuro es, a día de hoy, a tres años vista como máximo y con bastantes interrogantes que pueden influir en algunos cambios menores en las especificaciones que se han filtrado.

Lo que intentamos decir es que si esto ya de por sí casi atropella a la industria en post del avance, debemos de entender que seguramente los procesos litográficos se extiendan en el tiempo porque la industria necesita trabajar durante más tiempo para solventar los siguientes retos para seguir bajando nanómetros.

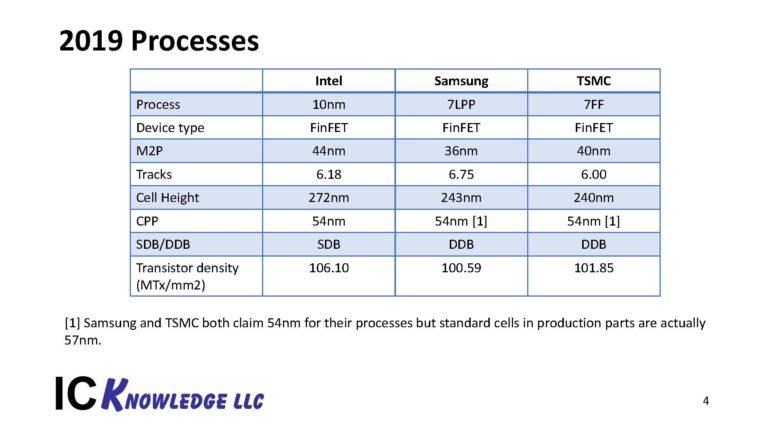

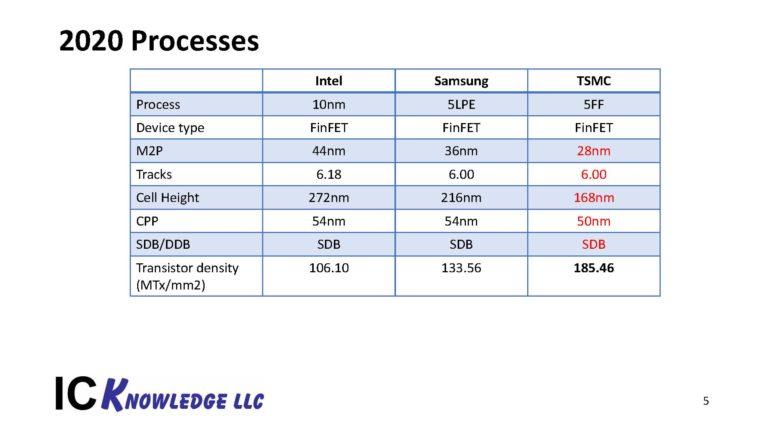

Esta tendencia se extenderá seguramente hasta 2030, donde es posible que estemos bordeando el átomo y ahí volveremos a enfrentar el siguiente problema. Entre tanto y echando la mirada atrás para tener un punto de partida claro, en 2019 Intel lanzó sus 10 nm, Samsung sus 7 nm LPP y TSMC sus 7 nm FF.

Aquí hay que matizar que aunque Intel tenía la delantera con su proceso litográfico, esta ventaja no era real como tal puesto que no se dispuso de la versión de alto rendimiento y por ello todo es un poco ficticio como tal.

Aunque Intel con sus 10 nm tiene mayor densidad, este 2020 tampoco será el año en el que debute como tal, en ningún sector, ya que la compañía pretende dar el salto a 10 nm ++ en 2021.

Este año 2020 todo va a cambiar drásticamente y aunque no se impongan los 5 nm de TSMC con una densidad realmente increíble de 185 millones de transistores por mm2, la realidad es que no entrarán directamente con productos de alto rendimiento igual que le ha pasado a Intel en 2019.

Samsung por su parte seguirá la estela de TSMC con un proceso menos denso pero seguramente más rentable por oblea. Intel sin mejoras en el horizonte y con la vista puesta en 2021.

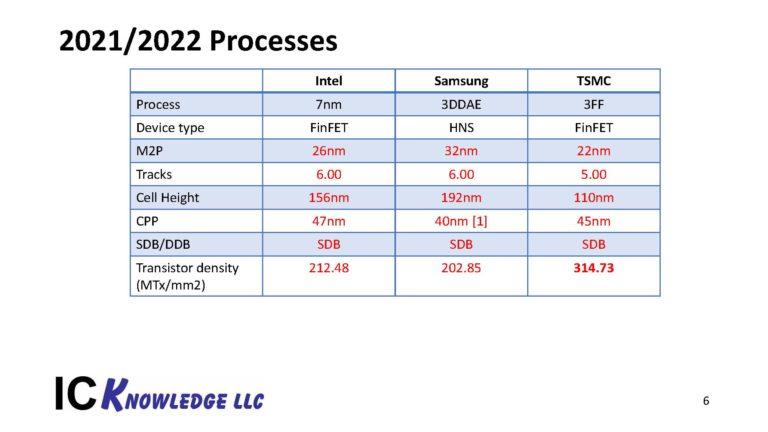

Siendo óptimos a la hora de hablar, hay que precisar que aunque las compañías afirmen lo mostrado en el gráfico, la realidad es que va a ser realmente complicado ver productos en dichos procesos litográficos más allá de que los estén produciendo en masa. Por ello se habla de 2022 como posible año de implementación.

Intel es posible que a finales de 2021 tenga sus 7 nm listos, pero TSMC casi con total seguridad no tendrá los 3FF para dicho año, en todo caso con vistas a 2022, ya que están enfrentando problemas que deben resolver primero.

En cambio, Samsung sí que podría tener sus 3 nm HNS para finales de dicho año y con vistas a productos finales a principios de 2022, donde podría hacer competencia a Intel en mayor o menor medida. En cualquier caso, esta industria es muy cambiante, donde hay adelantos puede haber retrasos, así que estaremos atentos para ver los cambios en tiempo real de los procesos litográficos.