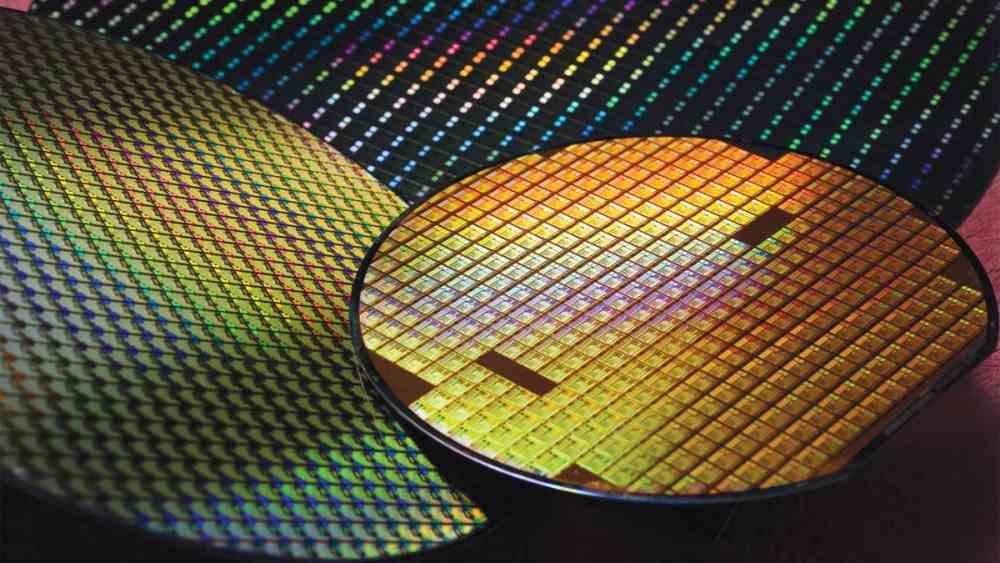

Todavía no ha aparecido ningún chip en el mercado fabricado con el nodo N3 o de 3 nm de TSMC, sin embargo, las últimas noticias son realmente malas, ya que un elemento que ha ido mejorando con el tiempo y tecnología tras tecnología se habría estancado definitivamente. ¿Se ha estancado definitivamente la SRAM?

La habitualmente mal entendida Ley de Moore ha sufrido varios anuncios de su final en los últimos años. Sin embargo, con el último anuncio de TSMC respecto su nodo de 3 nm, dicha afirmación podría convertirse en cierta. Al menos de cara a un tipo de combinación de transistores ampliamente utilizada en todo tipo de procesadores y esto resultará un freno al desarrollo de chips en los años siguientes.

Malas noticias: ya no pueden recortar el tamaño de la SRAM

Lo habitual con cada nuevo nodo de fabricación nos encontramos con que los transistores, tanto si son de lógica o de memoria, escalen a un menor tamaño. En el caso de la memoria, esto significa memorias internas de mayor tamaño o simplemente poder colocar más de ellas en el mismo espacio. Sin embargo, el nodo de 3 nm de TSMC trae consigo una noticia muy mala a la hora de escalar el tamaño de la SRAM respecto al nodo de 5 nm que se utiliza en la actualidad.

Pues bien, durante una conferencia en la edición número 68 del IEEE International Electron Devices Meeting (IEDM) donde se han reunido más de 1000 ingenieros de la industria, y, por tanto, la gente que diseña el hardware que usáis en vuestros PC, se discuten los desarrollados a corto y medio plazo de la industria. La gente de TSMC ha hablado de su nodo de 3 nm que usaran los futuros procesadores Ryzen y también los de Apple, así como la futura generación de tarjetas gráficas GeForce y Radeon. ¿Qué ha ocurrido? La fundición taiwanesa ha lanzado una muy mala noticia.

Para entender lo que está ocurriendo hemos de partir del hecho de que TSMC tiene dos variantes de su nodo de 3 nm.

- La primera llamada N3B puede fabricar SRAM con una densidad de 0.0199 micrómetros cuadrados por bit, una reducción de solo el 5% respecto al nodo de 5 nm,

- En cuanto a la otra variante, N3E, no existe escalado de ningún tipo. Lo que de entrada significa que el área ocupada por la SRAM dentro del procesador aumentará.

Se trata de una pieza esencial

Por el hecho que la SRAM se utiliza para construir las memorias internas que son esenciales para que funcionen los procesadores como son los registros y las cachés. Por lo que se trata de un elemento esencial y dicha limitación no podría poner en jaque muchos de los avances que se esperan para futuras generaciones de procesadores, donde la tendencia es el acercar la memoria al procesador con tal de poder disminuir el problema de la latencia y el consumo energético a la hora de mover los datos.

Así pues, al problema del movimiento de datos y el coste energético deberemos sumarle el del almacenamiento. No de cara a las memorias RAM dado que usan memoria DRAM, pero si dentro del procesador. Es decir, el tamaño de los cachés no aumentará y el añadido de nuevos núcleos será menor de lo esperado respecto al avance que hemos tenido en los últimos años, justo por esta limitación a la hora de escalar la memoria SRAM de un nodo a otro.

¿Es un problema único de TSMC?

Dado que Intel tomo recientemente la decisión de convertirse en una fábrica de chips no solo para sus productos, sino también para terceros, han entrado en una fiera competición con la fundición Taiwanesa para que otros fabriquen sus chips. Por el momento desconocemos la densidad de la SRAM en el nodo Intel 4 que será el que coincidirá en el tiempo en lo que a las piezas que van a salir al mercado. Aunque todo apunta que el proceso del fabricante estadounidense está un poco por debajo en cuanto a densidad de la SRAM.

En todo caso, todo ello apunta que el desarrollo de configuraciones de memoria 3DIC compuesta por varios chips apilados y que fue adoptada por AMD con los Ryzen X3D y la V-Cache será una solución más común a futuro de la que nos esperábamos y no un simple experimento, ya que será la única forma de implementar una caché de último nivel con la capacidad suficiente como para que la limitación en el escalado de la SRAM no resulte en un cuello de botella. El otro remedio es construir chips más grandes, pero con la subida de los costes está muy claro que el hardware, si ahora es caro, tiene el peligro de convertirse en un artículo de lujo.