TSMC muestra el chip con el que quiere competir con Intel y AMD en servidores

Estamos acostumbrados a la batalla entre Intel y AMD en todos los ámbitos posibles de CPU, donde en ocasiones alguna empresa intenta hacerles sombra dentro del sector HPC. Realmente todas las opciones actuales fuera de estas dos compañías pasan por ARM, donde ahora TSMC, el fabricante de obleas, demuestra querer entrar en este segmento a base de un diseño de chiplet a 7 nm ¿tienen que preocuparse Lisa Su y Swan?

TSMC diseña su chip basándose en ARM

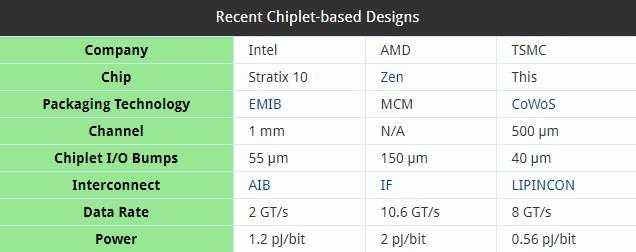

TSMC parece haber aprendido de lo que AMD ha hecho con su diseño en sus obleas y ha presentado un chip basado en chiplets, concretamente en un diseño de doble chiplet que puede escalar a un mayor número de ellos con los PHY adicionales que la empresa puede incluir en el diseño.

TSMC parece haber aprendido de lo que AMD ha hecho con su diseño en sus obleas y ha presentado un chip basado en chiplets, concretamente en un diseño de doble chiplet que puede escalar a un mayor número de ellos con los PHY adicionales que la empresa puede incluir en el diseño.

Por lo pronto, el diseño se basa en dos, pero lo hace en base a unas características que deben ser tomadas en cuenta:

- Quieren correr los núcleos a una frecuencia superior a los 4 GHz.

- Su BUS BiDir de interconexión superará los 4 GHz.

- CoWos y LIPICON a 8 GT/s y <1 pJ / bit.

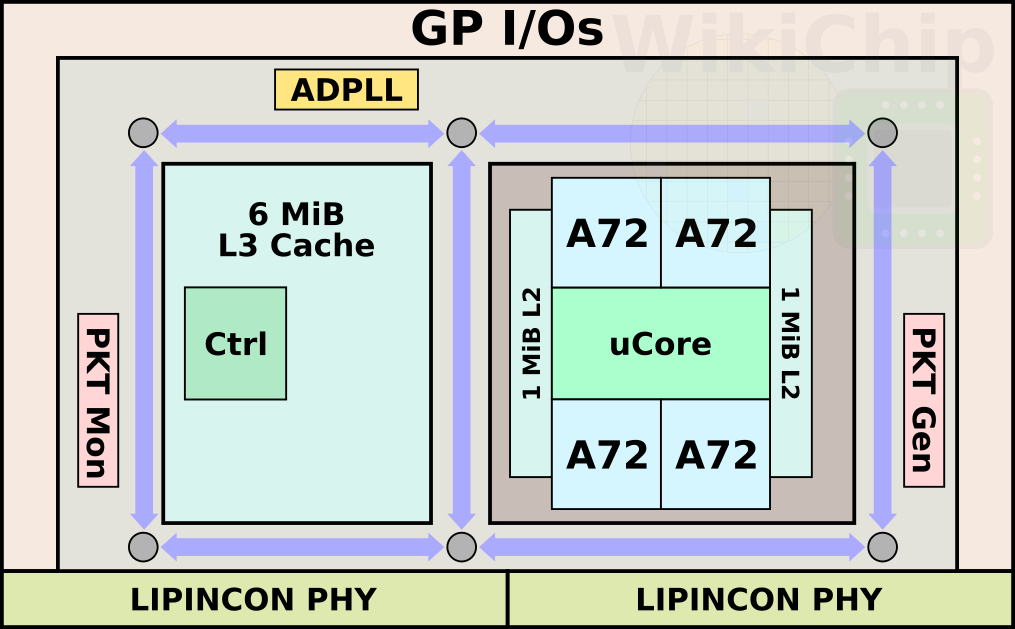

Para conseguirlo, cada chiplet se fabrica en 7 nm mediante 15 capas de metal, donde el área resultante es de solo 27,28 mm2. TSMC incorporó cuatro núcleos Arm Cortex-A72, donde incluirán una caché L1 diseñada a medida y optimizadas para frecuencias turbo por encima de los 4 GHz.

La L2 irá en el mismo encapsulado dividida en dos bloques, donde cada uno tendrá un tamaño de 1 MB, pero la L3 va totalmente aparte y se implementará usando celdas de bits de alta densidad, operando a un cuarto de la velocidad resultante.

Según TSMC, a 4 GHz su chip puede trabajar con un voltaje de 1.2 voltios, pero si escala hasta los 4.2 GHz el voltaje se dispara hasta los 1.375 voltios, lo cual hace presagiar que estamos cerca del muro de tensión.

Enlace entre chips: hasta 8 núcleos por CPU estando físicamente girados

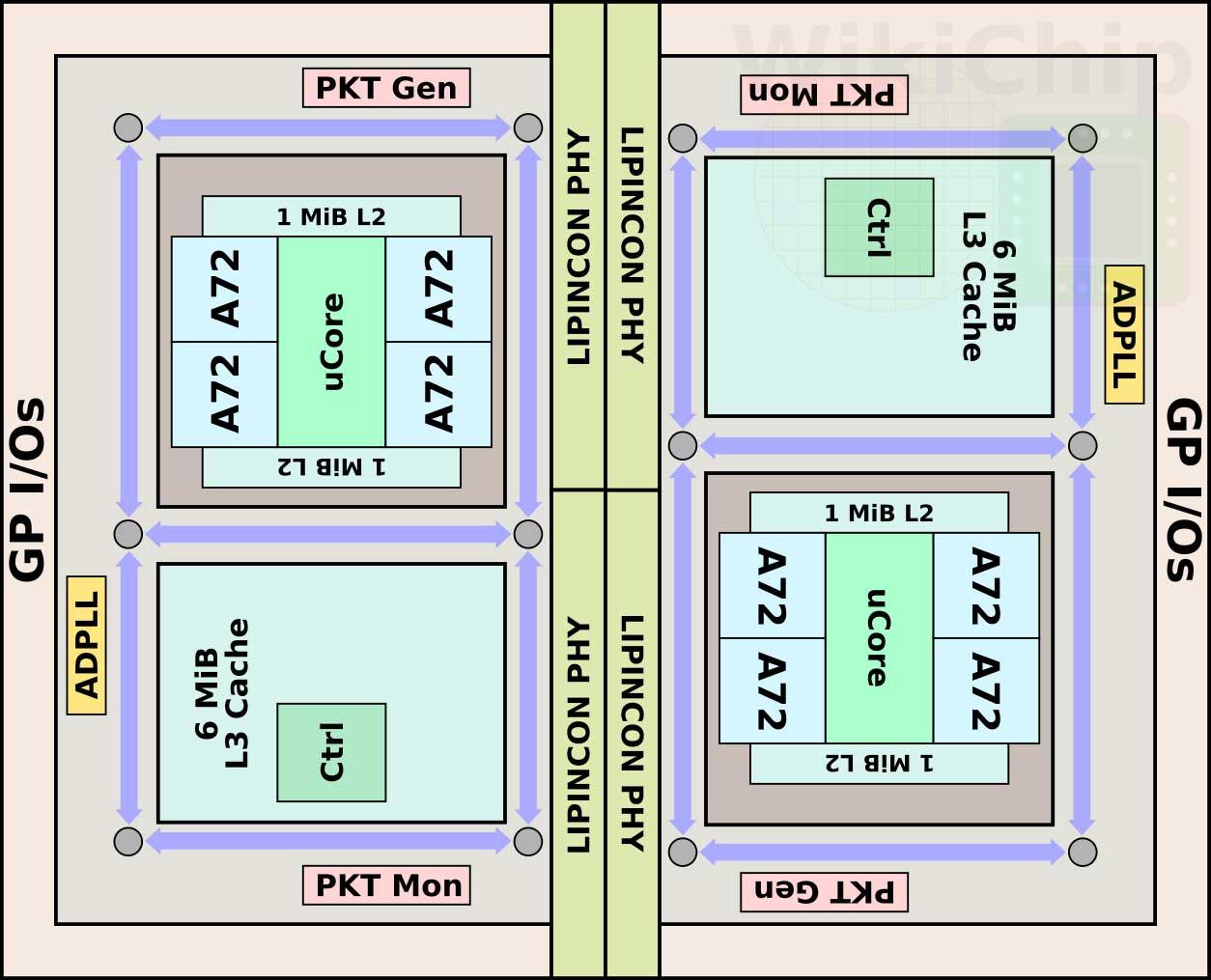

El concepto de TSMC es algo complicado de entender, pero tiene mucho que ver con el hecho de separar la caché L3 fuera de los núcleos Cortex. Cada paquete tiene dos conexiones PHY (LIPINCON), donde estas interfaces de conexión son de un solo extremo, unidireccionales y de baja latencia.

Lo curioso de la arquitectura es que una de estas interfaces sirve como maestro para que la CPU contigua y la L3 contraria se comuniquen, mientras que la otra conexión PHY es esclava y usa la dirección opuesta.

Para conseguir esto, los dos troqueles unidos entre sí tienen que disponer de uno de los chiplet girado 180 grados para así interconectar los LIPINCON PHY.

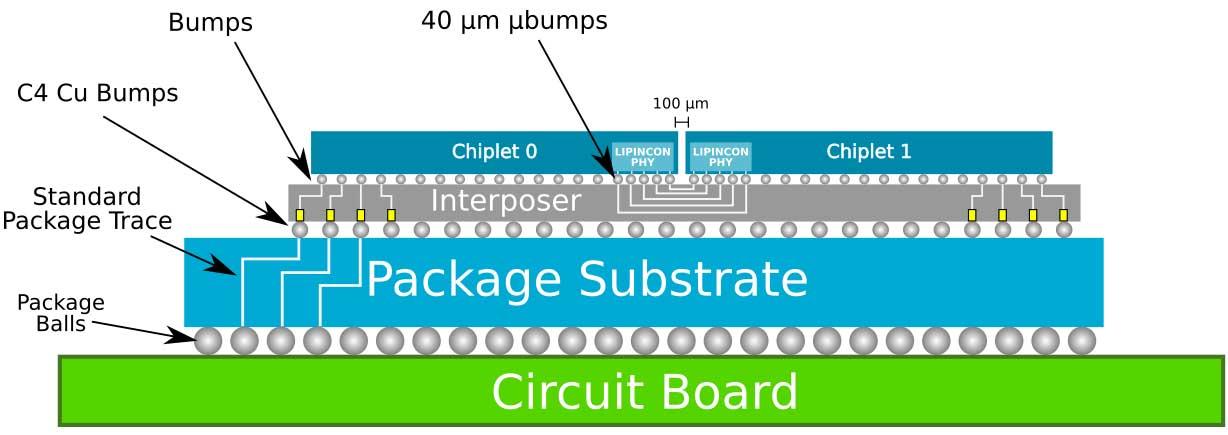

El diseño del chip como tal utiliza la tecnología CoWoS, de la que ya hemos hablado en otras ocasiones y que básicamente utiliza un interposer sobre el sustrato para interconectar con bumps los dos chiplets. La novedad aquí es el paso de solo 40 µm para interconectar los chiplets, donde la distancia entre ambos se ha reducido a solo 100 µm.

Para hacernos una idea, AMD usa µbumps de 150 µm, mientras que Intel en su Stratix 10 lo consiguió reducir a 55 µm.

Con estos nuevos chips TSMC pretende meterse de lleno en la lucha por el sector de HPC, muy selectivo en muchas ocasiones y con la ventaja de ser en ellas menos generalista, lo cual si consiguen un gran número de núcleos y una gran escalabilidad es posible que puedan poner nerviosos a los dos grandes, cosa que de entrada es harto complicada, ya que hablamos de gigantes de la supercomputación.