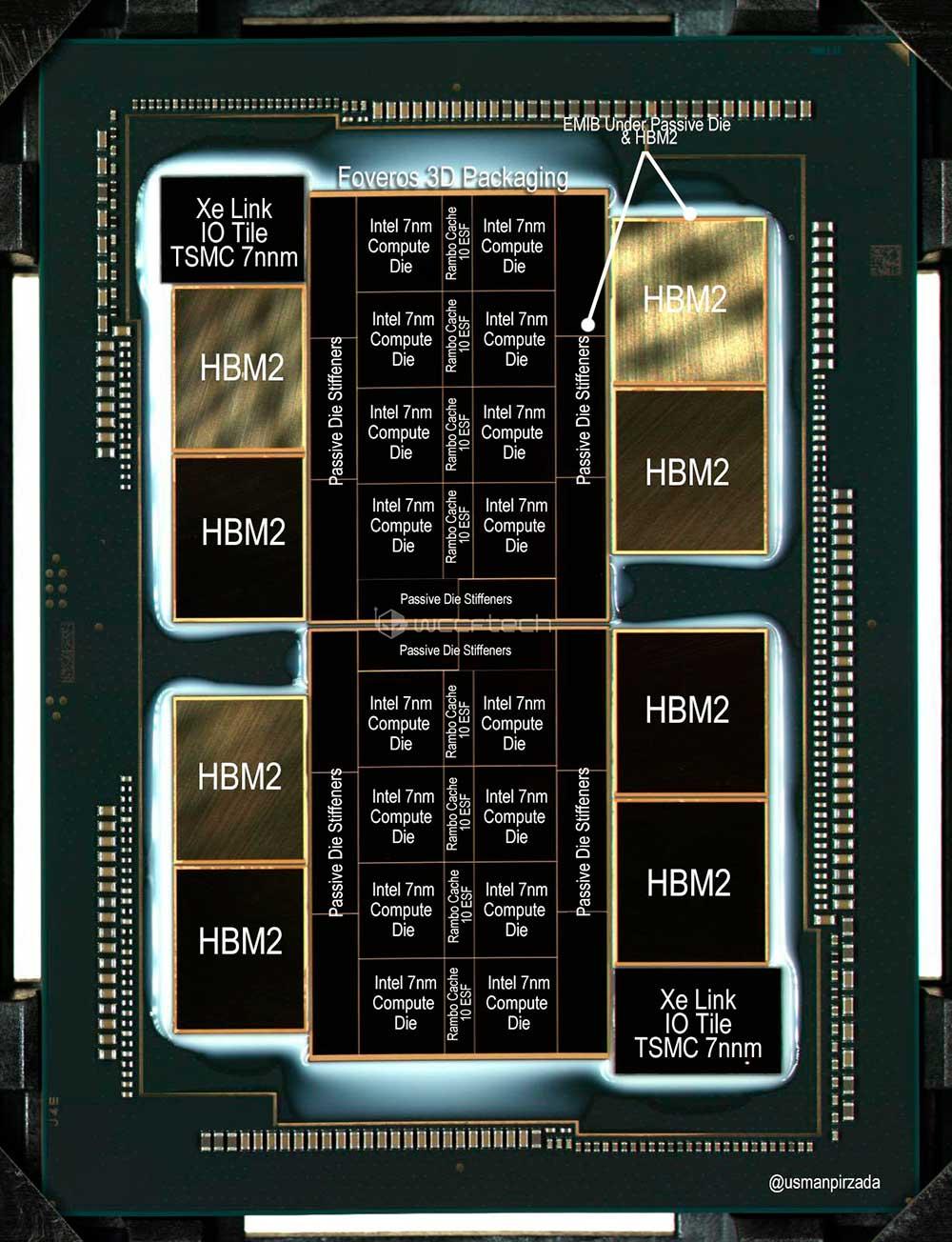

En el día de ayer el mismísimo Raja Koduri reveló el primer diseño de lo que será la primera GPU Ponte Vecchio de Intel dentro de su gama Xe HPC de alto rendimiento. Aunque la imagen estaba sombreada, los ingenieros se pusieron manos a la obra para discernir qué podría incluir Intel en lo mostrado, y la realidad sorprende … Principalmente por el número de dies, pero también porque hay 3 procesos litográficos en un solo package.

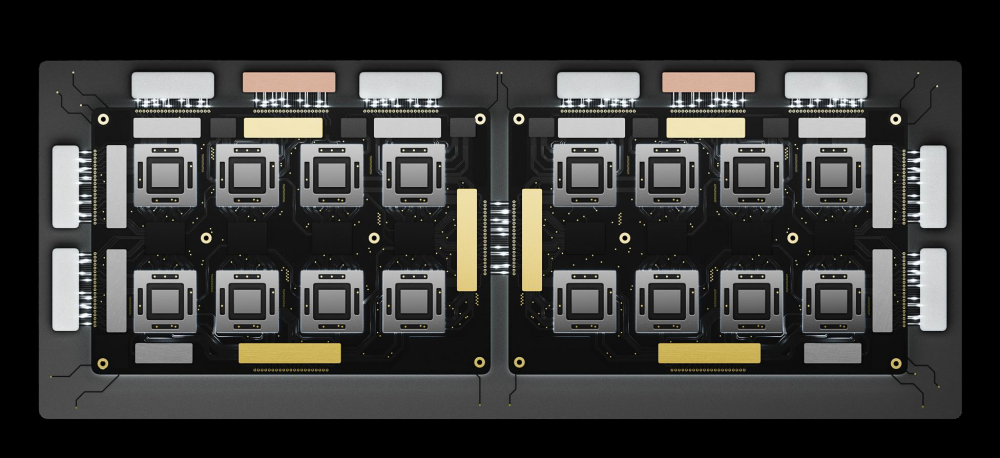

El chip presentado por Intel es, posiblemente, uno de los mayores logros de la ingeniería actual y al mismo tiempo, uno de los más grandes presentados en cuanto a tamaño. El hecho de contener dos tiles le otorga un privilegio en cuanto a tecnología punta, pero es que, si sumamos todo lo que se ha revelado, posiblemente estemos ante el chip más complejo jamás diseñado, y mucho más como GPU propiamente dicha.

Intel Ponte Vecchio GPU: tres procesos litográficos en un mismo encapsulado

Más allá del hecho de incluir dos matrices distintas y de estar interconectadas como tal, que ya de por sí es una gran novedad en el mundo de las GPU. Lo principal y que debemos tener en cuenta es que Intel ha dispuesto, al menos, de tres procesos litográficos distintos en sus nuevas tarjetas gráficas.

En primer lugar, tenemos la sorpresa de que los Die de computación no llegarán a 10 nm SuperFin como se dijo, sino que llegarán con sus más novedosos 7 nm, por lo que la densidad de estos será muy alta. En segundo lugar, tenemos el Xe Link IO fabricado por los 7 nm actuales de TSMC, por lo que Intel tendrá dies baratos con una densidad lógica muy aceptable y con una buena eficiencia, descargando a sus Fabs de dicha producción de un die de interconexión, que si bien es vital, dentro de su gremio es algo secundario.

Otra de sus curiosidades es el hecho de encontrar varios dies de HBM2 (y no HBM2E como se especulaba), ya que estos dies tienen dos tamaños totalmente distintos. Falta confirmar en este aspecto las pilas que integrarán, para así saber la cantidad total de memoria VRAM que poseerán, pero los rumores apuntan a un mínimo de 32 GB.

Dies pasivos para interconexión y Rambo Caché

Lo más llamativo sin duda son los dies pasivos y el hecho de que Intel por fin incluya su Rambo Caché en GPU. Los primeros son necesarios para la interconexión de los tiles, aunque no se ha revelado el entramado interno ni por capas, sí sabemos que no incluyen lógica alguna en su interior más allá del cableado correspondiente y sorprende el tamaño total en área que necesitan.

La Rambo Caché está integrada entre los dies de computación para minimizar la latencia y estará fabricada por el actual nodo de 10 nm SuperFin de Intel. Hay serias dudas sobre el hecho de por qué Intel no las ha fabricado a 7 nm bajo EUV, pero es posible que al ser un apartado menos complejo que los de computación, Intel haya optado por escoger un proceso ya maduro y supuestamente barato para el año que viene para su creación.

Lo que sí sabemos ahora es que Raja Koduri no mentía cuando dijo que había 7 tecnologías avanzadas en esta GPU con 2 tiles:

- Intel 7nm

- TSMC 7nm

- Foveros 3D Packaging

- EMIB

- Enhanced Super Fin

- Rambo Cache

- HBM2

Pero al mismo tiempo también se rumorea que no estamos ante la versión de mayor capacidad y rendimiento de Intel, así que podríamos tener un chip masivo de mayores prestaciones en no demasiado tiempo. En cualquier caso y visto lo avanzado del proyecto, parece que Intel sí que cumplirá con los plazos fijados en su roadmap, tanto de I+D como de desarrollo propio en sus Fabs ya entrando en el apartado más físico.

No en vano, si se retrasasen estas GPUs su proyecto Aurora como supercomputador número 1 del mundo tendría que dejarse parado hasta que las tarjetas gráficas Ponte Vecchio estuviesen lista, algo que no se pueden permitir.