La litografía en los chips que se utilizan en los procesadores tal y como los conocemos está desde hace tiempo en una lucha para reducir sus procesos de fabricación, y estamos viendo como los nanómetros se van reduciendo cada vez más. Sin embargo, cuando se trata de memoria 3D NAND, está «atascada» en 40 nm desde hace ya bastante tiempo, y la tendencia es que siga siendo así al menos a medio plazo. ¿Por qué no mejoran la litografía de la memoria? Te lo contamos todo a continuación.

La tecnología 3D NAND se introdujo por primera vez en 2013, y Samsung hizo una gran labor de mejora de la misma en el año 2015; sin embargo, desde entonces ni Samsung ni sus competidores han introducido nuevas mejoras en esta memoria más allá de crear más y más capas para aumentar la densidad. Así pues, si la memoria 3D NAND es de 40 nm, ¿por qué no vemos mejoras con nodos más pequeños como 32 nm, 20 nm, etc.?

La respuesta es que resulta casi imposible reducir la litografía por culpa de cómo se fabrican, concretamente, los canales de comunicación entre capas y te lo vamos a explicar a continuación.

Así se fabrican los canales de la 3D NAND a 40 nm

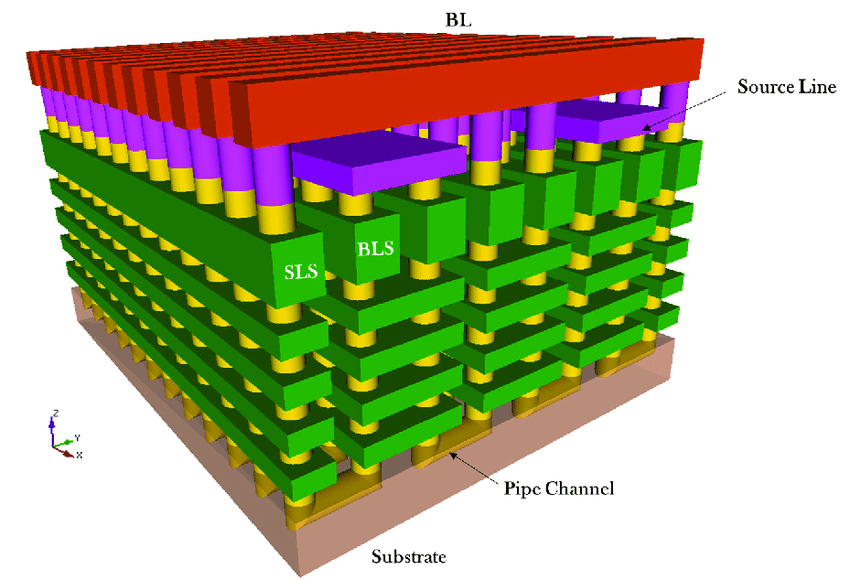

Para explicar por qué no se puede reducir mucho más la litografía de la memoria 3D NAND vamos a utilizar como ejemplo la estructura BiCS de Toshiba (ahora usada por KIOXIA).

- Primero, se realizan agujeros muy estrechos en todas las capas de la 3D NAND. Hoy en día estos agujeros tienen una relación de aspecto de aproximadamente 60:1, lo cual es bastante notable. Pensad que para esta litografía, un agujero de una pulgada (2,5″) de diámetro tendría 1,5 metros de largo. Estos orificios son así, con paredes casi perfectamente paralelas de arriba a abajo que atraviesan todas las capas de material y que sirven para comunicar todas entre sí.

- Luego estos agujeros se rellenan con gran precisión con 5 capas de material:

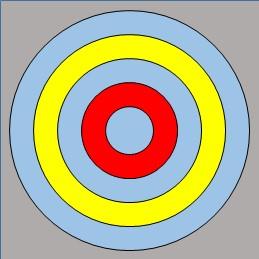

- La capa inicial es de óxido de silicio (SiO2), que hace el agujero todavía más estrecho. Esto se muestra en color azul pálido en el diagrama que os vamos a poner más abajo.

- Luego, se cubre con otra capa fina de nitruro de silicio (Si3N4) también de arriba a abajo, haciendo el orificio todavía más estrecho. Esta es la capa de captura de carga y se muestra en amarillo.

- Hay una tercera capa muy delgada de SiO2, lo cual hace el agujero todavía más estrecho.

- La siguiente capa es de polisilicio conductor. Esta capa se muestra en rojo y sirve como canal de transmisión de datos.

- Finalmente, el poco espacio que queda se rellena con SiO2 (azul) de nuevo. Este relleno aislante final ayuda a «adelgazar» el canal para que tenga un mejor comportamiento y sea más estable.

Así pues, el grosor de las capas que rellenan los agujeros determinan su diámetro mínimo, y aunque aquí lo hemos mostrado en «grande» en realidad el grosor de cada capa interna es de solo unos pocos átomos de espesor y es prácticamente imposible hacerlos más pequeños.

Por este motivo la memoria 3D NAND deberá permanecer en 40 nm en el futuro previsible, y por eso todo el ahínco de los fabricantes en los últimos tiempos es aumentar la cantidad de capas que atraviesan estos agujeros de comunicación, la lógica dentro de la matriz y las configuraciones mejoradas de escalera, pero no en reducir la litografía porque en este momento es físicamente casi imposible.