La implementación de la Infinity Cache en las GPUs con arquitectura RDNA 2 ha sido una de las novedades de la nueva arquitectura de GPUs de AMD, pero la pregunta que nos viene a la cabeza es: ¿es algo exclusivo de las GPUs de AMD o vamos a verlo los procesadores Ryzen, tanto en CPUs como en SoCs?

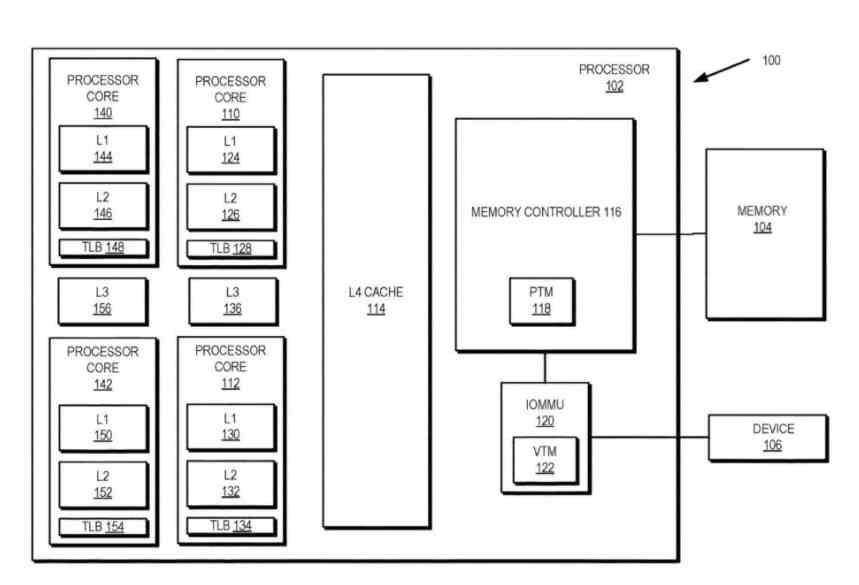

Hace unos meses se filtró el diagrama de una patente de AMD, el cual correspondía a un procesador de la familia AMD Ryzen, o al menos eso suponemos, pero con la particularidad de mostrar una cache de cuarto nivel en el diagrama, algo inédito en los procesadores de AMD basados en dicha arquitectura.

Al mismo tiempo la aparición de la Infinity Cache en las GPUs de AMD nos trae dos preguntas a la cabeza: ¿vamos a ver implementada la Infinity Cache en los procesadores AMD Ryzen de AMD, lo hará como cache L4 o de alguna otra forma?

El conflicto de utilidad de la Infinity Cache y la Cache L3 de los núcleos Zen

Tanto la cache L3 de los núcleos Zen como la Infinity Cache de la arquitectura RDNA 2 cumplen la misma función, ya que ambas son Victim Caches y por tanto tienen la misma funcionalidad. Esto significa que a la hora de captar los datos e instrucciones para cada uno de sus procesadores correspondientes, sino que se encargan de recoger las líneas de cache descartadas por el nivel de cache anterior.

¿Cuál es el problema? Para entenderlo hemos de tener en cuenta donde iría la Infinity Cache de estar implementada tanto en un SoC como en una CPU de AMD, justo antes del controlador de memoria y por tanto en el Northbridge, como una supuesta cache L4.

¿Cuál es el conflicto? No tiene sentido que haya una Victim Cache de otra Victim Cache, ya que en este caso la Infinity Cache estaría conectada a la cache L3 de los núcleos Zen, lo que provoca un conflicto de funciones entre ambas partes.

El conflicto de conectividad de la Infinity Cache con los núcleos Zen

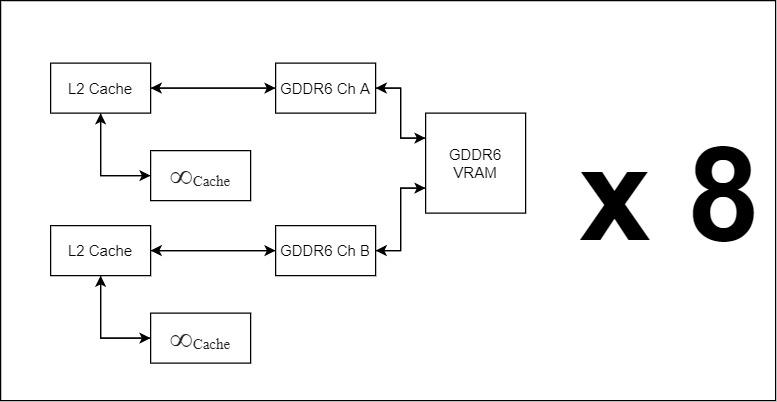

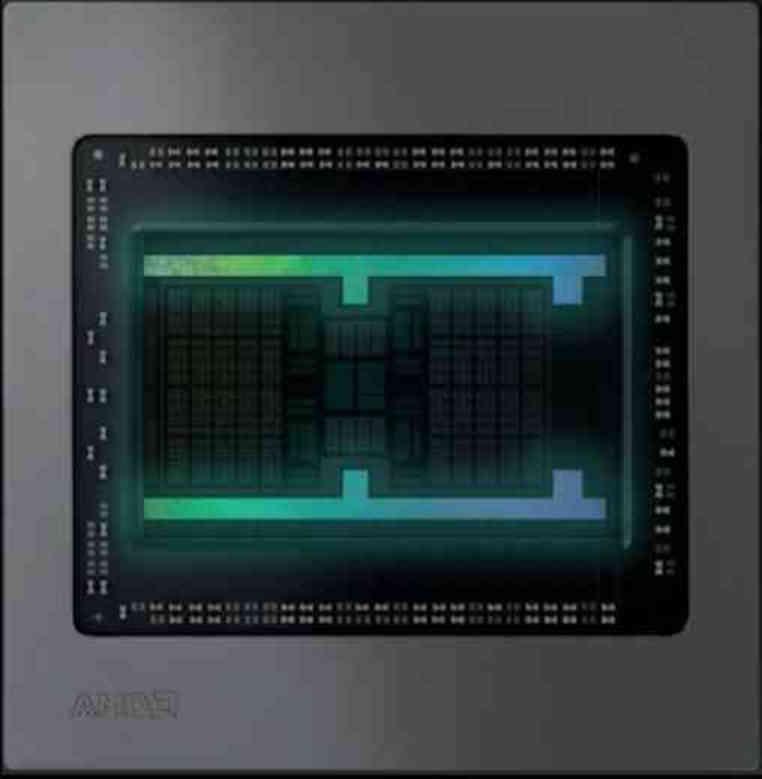

Si nos fijamos en la Infinity Cache de la GPU Navi 21 nos encontramos que son 16 particiones en total, conectadas en un extremo a 16 particiones de cache L2 bajo un bus de 64 bytes/ciclo por cada partición y en el otro extremo a 16 canales GDDR6.

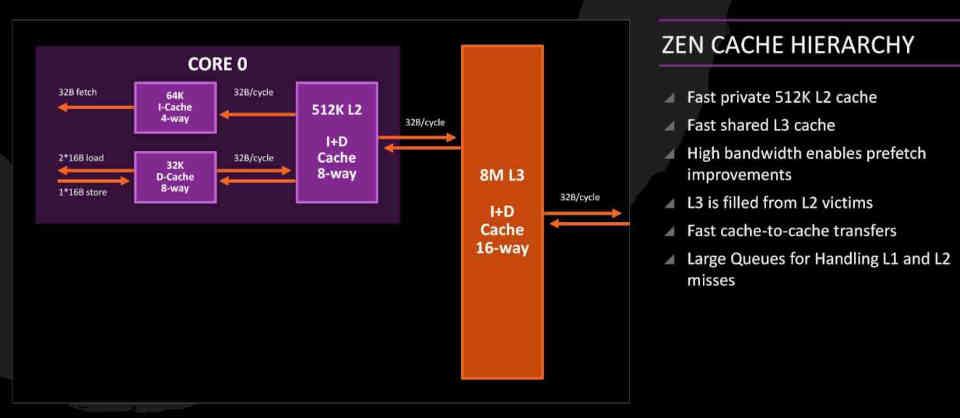

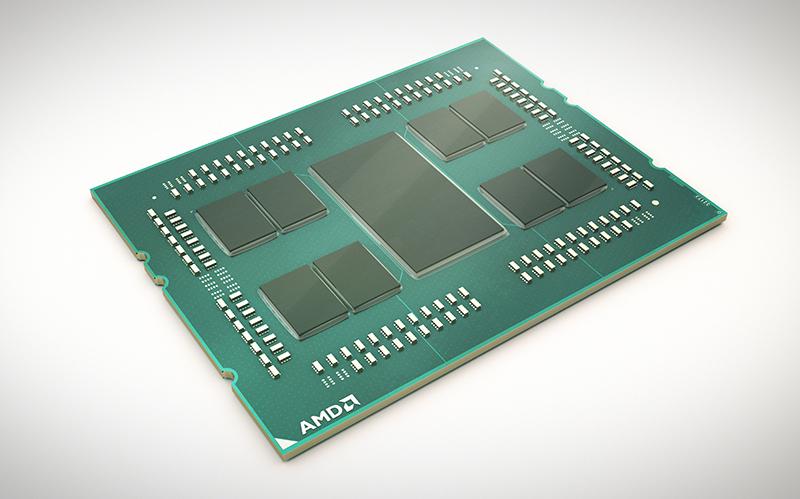

Los núcleos Zen de los procesadores Ryzen se agrupan en un CCXs de 4 (Zen y Zen 2) u 8 núcleos (Zen 3), pero el CCX utilizan una sola interfaz Infinity Fabric, por lo que la supuesta Infinity Cache en un procesador Zen solo estaría compuesto por una cantidad de particiones igual a la cantidad de CCXs como mínimo.

Por lo que en una configuración con un CCD solo tendría una partición, una con dos particiones 2 CCDs y el caso extremo sería algo como un AMD Epyc con 8 CCDs que tendría 8 particiones. Por norma general, las caches aumentan de tamaño con cada nivel adicional y siempre es el doble del sumatorio del nivel anterior de cache.

Un solo CCD de Zen 3 tiene una capacidad de 32 MB de Cache L3, una sola partición de la Infinity Cache son 8 MB, una cifra muy inferior que la que necesitaría para operar como Cache L4 de un procesador Zen, por lo que en conectividad queda demostrado que la Infinity Cache no puede funcionar como Cache L4 de un procesador con CPU Zen.

¿Y qué hay de las GPUs integradas?

Ya que hemos visto como la Infinity Cache no es posible utilizarla como cache adicional de los núcleos Zen, la única respuesta que nos queda es como Infinity Cache de los núcleos RDNA 2 integrados en los SoCs, por el momento AMD no ha lanzado ningún SoC con una GPU de arquitectura RDNA integrada, por el timing de lanzamiento no creemos que vayamos a ver la primera generación de RDNA.

En el caso de las iGPUs sí que tiene sentido integrar una Infinity Cache que se sitúe entre el controlador de memoria y el procesador gráfico, pero sería de uso exclusivo para el procesador gráfico dentro del SoC.