La futura llegada de los procesadores basados en chiplets trae consigo una pregunta: ¿qué interfaces y protocolos se utilizarán para comunicar los diferentes elementos de un chiplet entre sí? Pese a que habrá varios distintos y uno por cada marca, la Common Electrical I/O en dos de sus variantes es la interfaz de comunicación que se utilizará para la comunicación de los chiplets encima de un interposer.

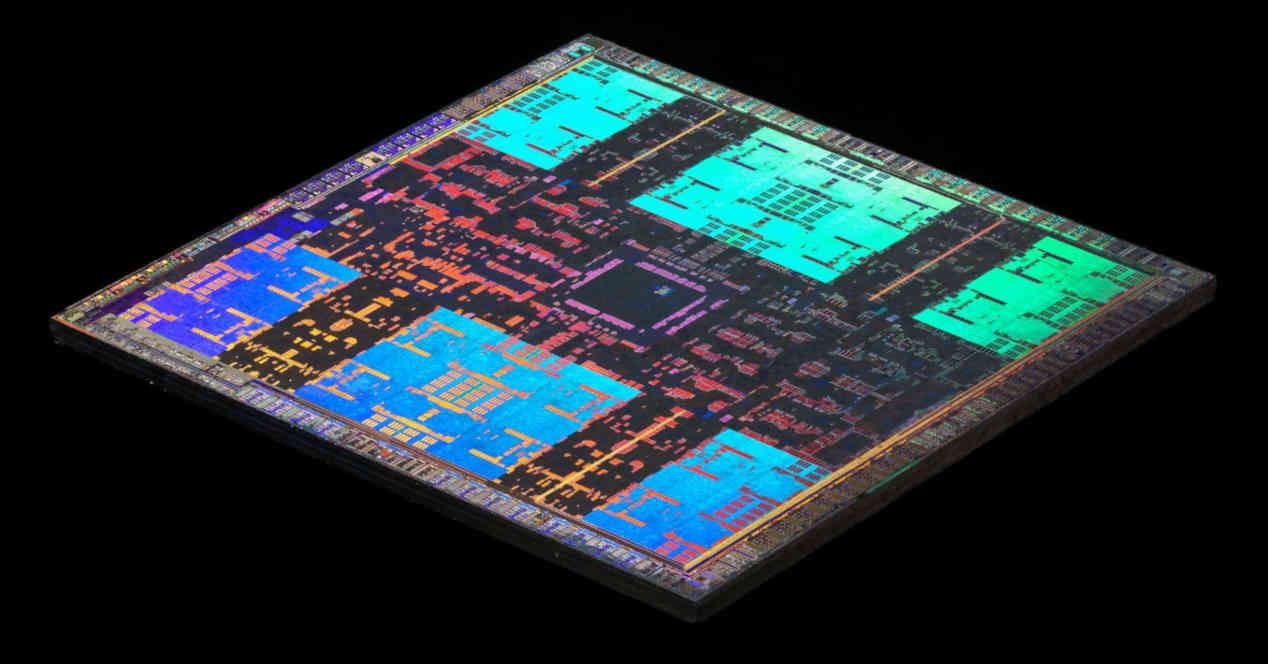

No hay ninguna duda que los procesadores compuestos por chiplets van a ser la norma en los años siguientes, sabemos que va a ser la apuesta de futuros diseños tanto de Intel, AMD y NVIDIA, en los que cada una de ellas ha desarrollado una interfaz propietaria para la comunicación para el uso con sus arquitecturas.

La Common Electrical Interface en cambio, es la interfaz que se está estandarizando para la comunicación entre los elementos en un chiplet y que no es propietaria de esas tres compañías. Es más, muchos de los diseños se construyen unidades FPGA que hacen uso de dicha interfaz para comunicar las diferentes partes. Aunque antes de explicaros en que consiste, lo mejor es dar un periplo a través de una serie de conceptos básicos.

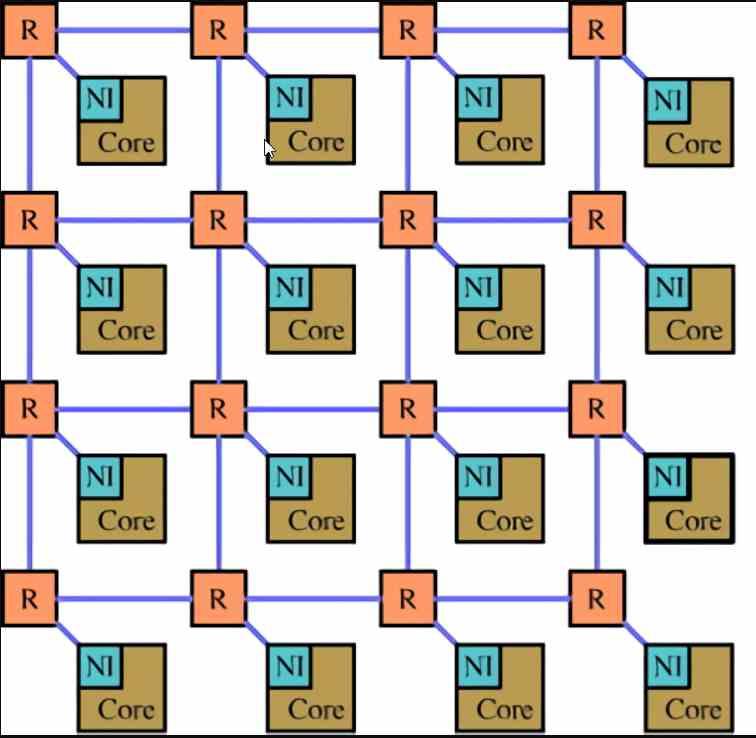

El concepto de NoC

NoC o red en un chip, es la idea de hacer una intercomunicación entre los varios componentes del PC como si de una red se tratará, para ello cada uno de los elementos tiene un enrutador que lo comunica con los otros elementos, por lo que solo es necesario que cada elemento de la red tenga integrado un router que sirve para comunicar y comunicarse con el resto

Cada elemento dentro de la red de componentes tiene una dirección propia y la forma de comunicarse entre los diferentes componentes es hacer que cada elemento llame a la dirección de red de otro elemento, en la cual no solo los elementos de procesamiento tienen una dirección dentro de la misma, no solo los procesadores e interfaces de E/S, sino también las memorias que la componen, ya sea memoria RAM, VRAM e incluso chips NVMe con tal de facilitar la comunicación.

La idea de un MCM como NoC

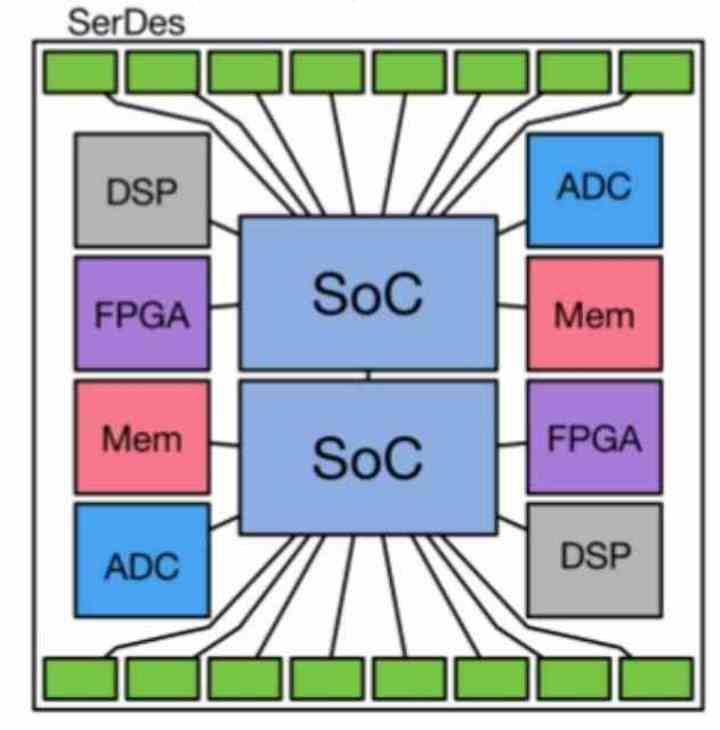

Algo que diferencia un SoC de un MCM es que en el primer caso tenemos una unidad central en el chip que se encarga de comunicar entre sí todos los elementos dentro del chip y estos con la memoria es común en todos los SoC, independientemente de cuál sea la arquitectura de la que hablemos, todos los SoC contienen ese elemento en común.

Pero en un MCM compuesto por varios elementos por separado tiene que haber también una unidad que se encargue de comunicar los diferentes elementos entre sí. Si hablamos de un SoC entonces tiene que haber una misma unidad encargada de la comunicación, pero en el caso de que hablemos de un NoC en el que cada elemento se puede comunicar con otro de manera directa entonces la cosa ya cambia.

En un NoC la comunicación es realizada entre los diferentes elementos utilizando una interfaz de red, imaginad esto como red LAN, pero utilizando conexiones mucho más rápidas para la comunicación entre los diferentes elementos del chiplet, por la corta distancia y el material utilizado.

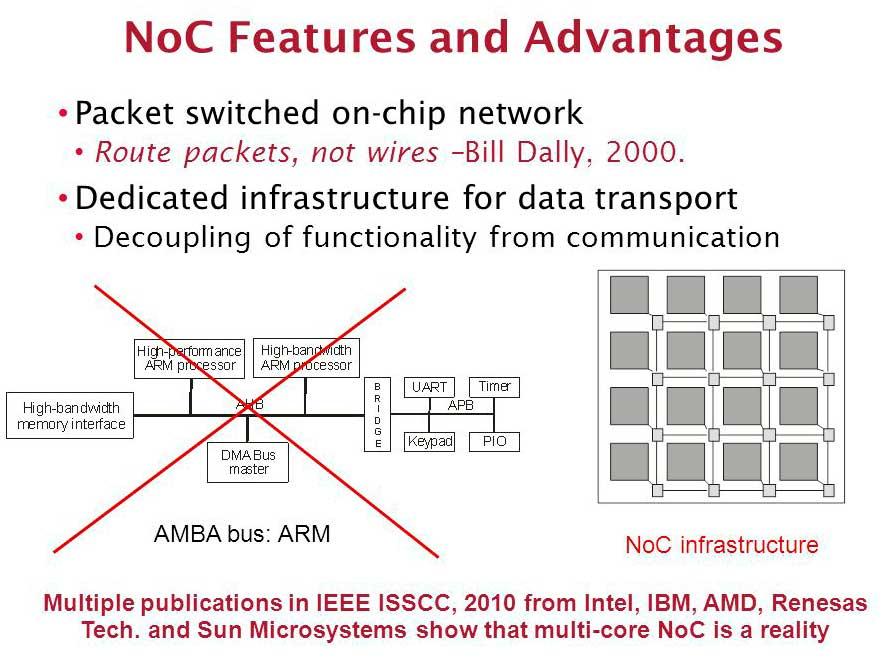

¿Qué es la Common Electrical I/O?

The Common Electrical I/O acortado como CEI, es una serie de acuerdos realizados por un consorcio llamado Optical Internet working Forum (OIF), el cual se encarga de definir los requisitos comunes para las interfaces eléctricas con una velocidad de comunicación con una velocidad de transferencia de 3.125, 6, 11, 25-28 y 56, 112 y pronto 224 Gbps.

La CEI ha sido la base para diferentes tipos de interfaces de E/S y de protocolos como el Hyper Transport del que deriva el Infinity Fabric de AMD, la interfaz SATA en varias de sus versiones. Como son las interfaces 803.3 e InfiniBand.

Su importancia es debido a que mientras Intel y AMD van a utilizar sus propias interfaces propietarias para comunicar los diferentes chiplets dentro del MCM, es sumamente importante la existencia de una interfaz estándar que se pueda utilizar no solo de cara a poder desplegar diseños basados en chiplets por parte de diferentes diseñadores de procesadores, sino también para el desarrollo de estos.

El Common Electrical I/O se trata de una interfaz del tipo SERDES, que en su versión actual puede alcanzar la velocidad de 112 Gbps de transferencia. En la actualidad tiene diferentes variantes, pero las que nos interesan son las que están relacionadas con los chiplets, ya que van a ser ampliamente utilizadas para la comunicación entre los diferentes elementos.

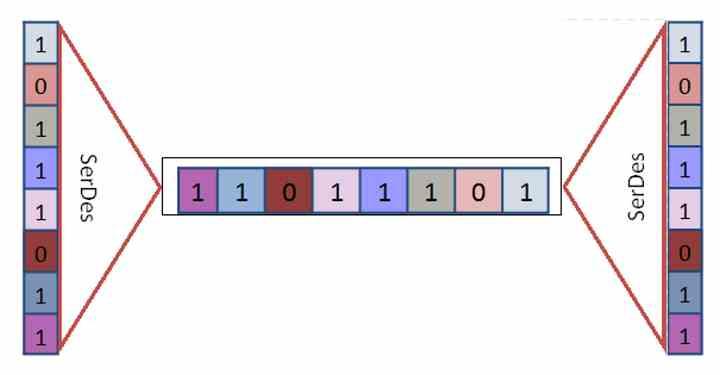

Un SERDES es un tipo de interfaz que lo que hace es tomar una serie de datos en paralelo y transmitirlos en serie a otra igual que hará el proceso contrario, es decir, convierte una señal en serie en una en paralelo de nuevo. De ahí la acotación de SERDES.

En el caso de la actual interfaz de 112 Gbps, este utiliza una codificación del tipo PAM4, de tal manera que puede alcanzar los 112 Gbps de velocidad haciendo uso de una velocidad de reloj de 28 GHz para la comunicación. Tales velocidades de reloj serían sumamente contraproducentes si hablamos de grandes distancias, pero no es el caso de un MCM compuesto por chiplets con un interposer por debajo, en el que los diferentes elementos están a muy poca distancia para poderse comunicar.

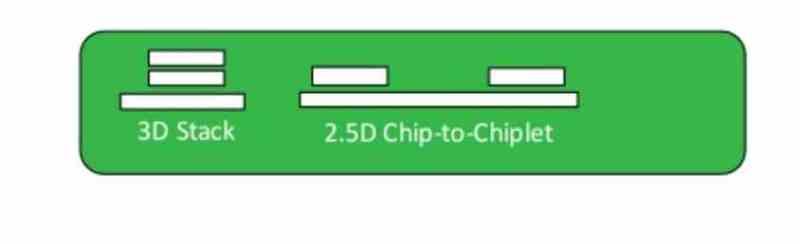

Dentro de la interfaz Common Electrical I/O tenemos dos tipos, por un lado tenemos la que se encarga de la comunicación en un chiplet tradicional, la cual en su versión a 112 Gbps recibe el nombre de CEI-112G-MCM y está pensada para cableado con una distancia entre ambos extremos de como mucho 2.5 mm, la poca distancia del cable le permite consumir muy poca energía por transferencia.

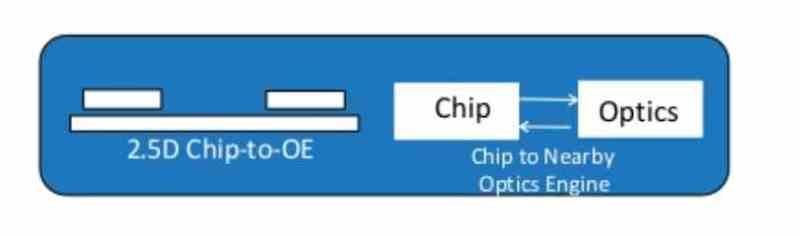

El segundo tipo está pensado para la comunicación con un receptor óptico, y si, el próximo paso después de los interposers convencionales es utilizar interfaces ópticas para la comunicación, aunque por el momento estas no se utilizan ni se utilizarán a corto plazo en sistemas domésticos.

Common Electrical I/O para la comunicación externa de los chiplets

Un chiplet pese a estar formado por diferentes unidades en su interior, puede ser visto como una sola unidad de cara al exterior y la forma con la que se comunica es a través de una serie de interfaces de E/S que dan conectividad.

Claro esta que para la comunicación dentro del chiplet, este tipo de interfaces externas necesitan ser transformadas en una señal del tipo Common Electrical I/O, a través de una serie de SERDES que se encuentran cercanos a la periferia del chip. Justo antes de las interfaces externas, ya sean hacía la memoria RAM, VRAM, interfaces PCI Express, etc.

De esta manera el Common Electrical I/O se convierte en la interfaz de intercomunicación para comunicar diferentes interfaces de E/S entre sí.