Hace ya cinco años de la compra de Altera por parte de Intel, cuya tecnología ha sido eficientemente integrada en el catálogo de la empresa fundada por Gordon Moore. La que ha sido históricamente la competencia de Altera, Xilinx, está a punto de ser adquirida por AMD en lo que se puede convertir en una de las adquisiciones más importantes del sector en los últimos años. ¿Cuáles son las causas y las consecuencias? ¿Cómo va a afectar al usuario medio de PC? ¿A qué viene el interés de AMD para adquirir Xilinx?

Existen mercados donde nos encontramos que la competencia directa de AMD, Intel en procesadores y NVIDIA en tarjetas gráficas, tiene una presencia mucho más grande que los de rojo y es en este punto donde el catálogo tecnológico de Xilinx aporta mucho a la empresa dirigida por Lisa Su, ya que les va a permitir llegar a mercados a los que antes no podían llegar, con soluciones que antes no podían implementar.

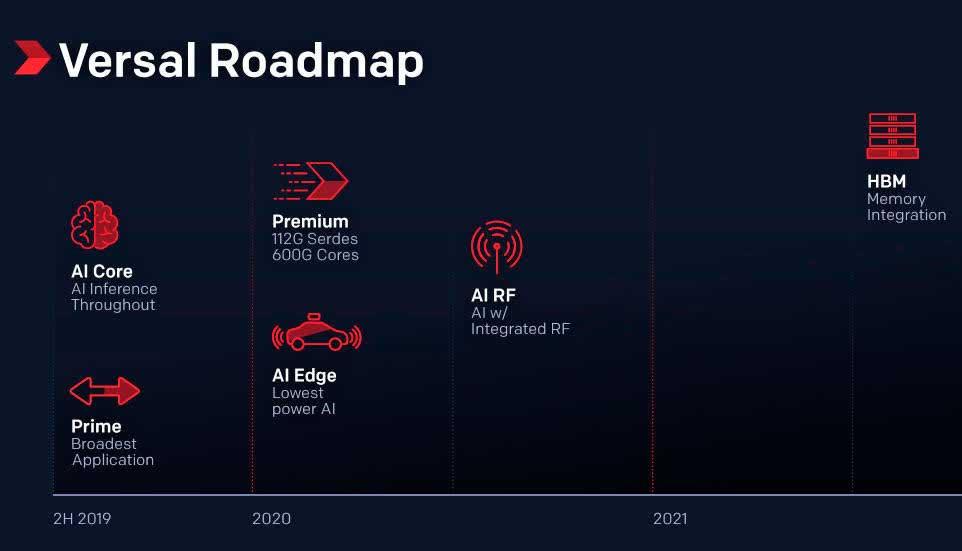

¿Y qué puede aportar Xilinx a AMD? Pues una formidable presencia y tecnología punta en 5G, redes, automóviles inteligentes y especialmente en cuanto a comunicaciones, mercados en los que AMD no tiene presencia por el hecho que el desarrollo de sus tecnologías no ha ido en ese sentido, pero la cosa es mucho más profunda y requiere un análisis detallado.

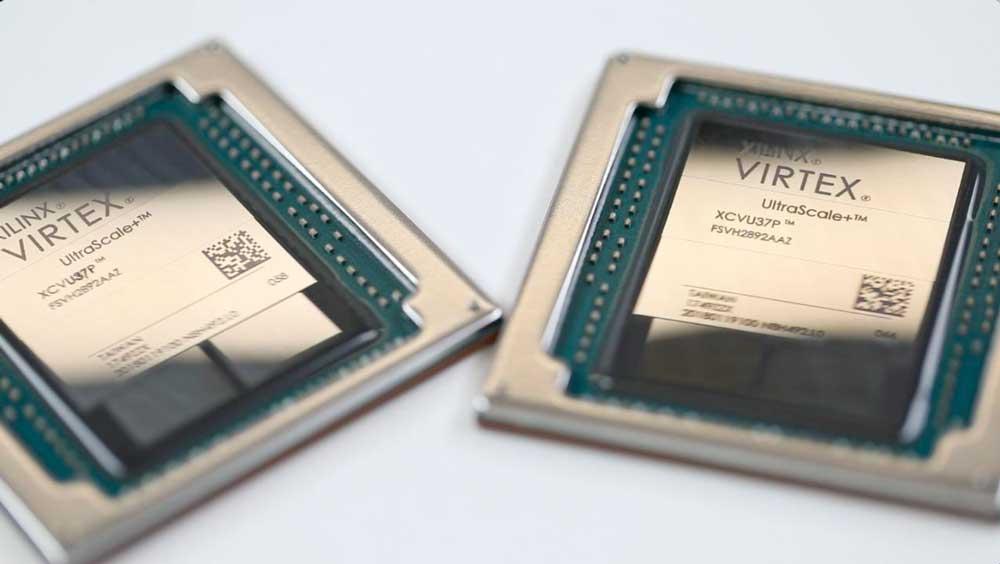

Los FPGA llegan a AMD de la mano de Xilinx

Hay que tener en cuenta que Xilinx es una empresa especializada en el desarrollo de los FPGA, aunque aparte de ello también licencian código de descripción del hardware como IPs que cargar en sus FPGA y que tienen funciones específicas dentro de diferentes ámbitos.

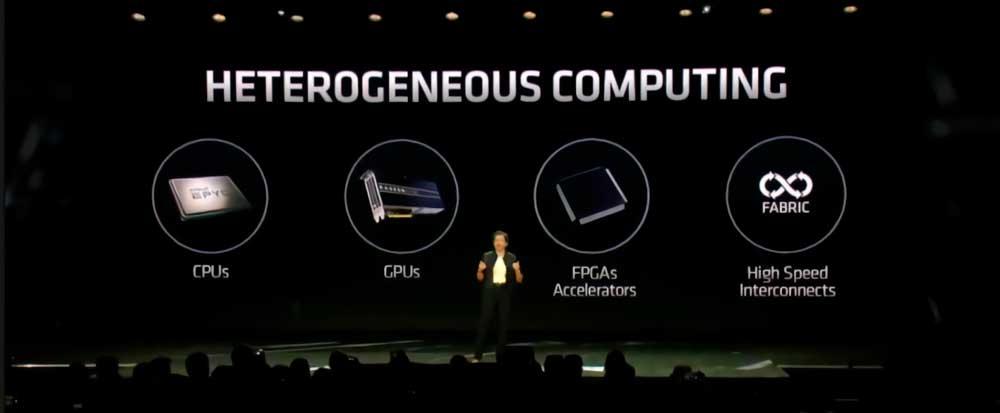

Podemos comparar esta compra como la que AMD realizó en su día de ATI Technologies; la idea de implementar la tecnología de Xilinx en los procesadores de AMD la dejó caer de manera muy sibilina Lisa Su en el CES de 2019, en el que en una de las diapositivas aparecía el concepto «FPGA Accelerators». Desde entonces no hemos vuelto a saber nada por el mero hecho que AMD no tiene una división de FPGAs que le permita desarrollarlos.

Antes de nada, hemos de entender lo que es el concepto de acelerador: son co-procesadores que se dedican a hacer tareas específicas dentro de un procesador, pero las hacen utilizando un área del chip mucho más pequeña que un procesador completo y con un consumo muy pequeño.

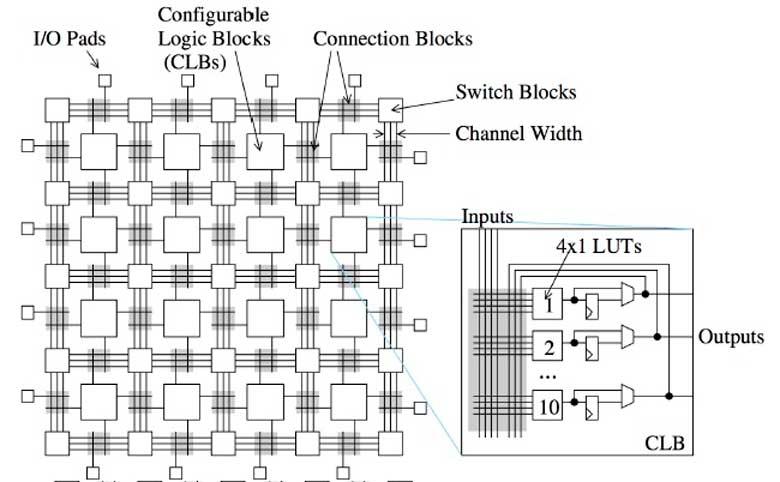

Un ejemplo de este tipo de aceleradores puede ser un descodificador de vídeo integrado dentro de un SoC o una GPU; el problema de dicho descodificador es que si aparece un nuevo tipo de formato de vídeo no podemos cambiar la circuitería del mismo para que lo pueda reproducir, pero con un FPGA a cambio de que estos son un poco más complejos en tamaño sí que pueden ser reconfigurados para soportar nuevos estándares o mejorar su eficiencia.

La otra ventaja es que nos permite reorganizar por completo el propósito dentro de los diferentes aceleradores. Imaginad que tenemos un controlador de pantalla implementado vía FPGA en el SoC, pero solo vamos a utilizar un monitor o hay interfaces que no vamos a utilizar. Pues a nivel de usuario podemos hacer que el controlador de pantalla cargue una IP más simple y las puertas lógicas de la parte o partes FPGA puedan ser utilizadas para otras tareas que tengan mucho más sentido de cara a las necesidades de cada cliente.

La influencia de los FPGA de cara a la inteligencia artificial

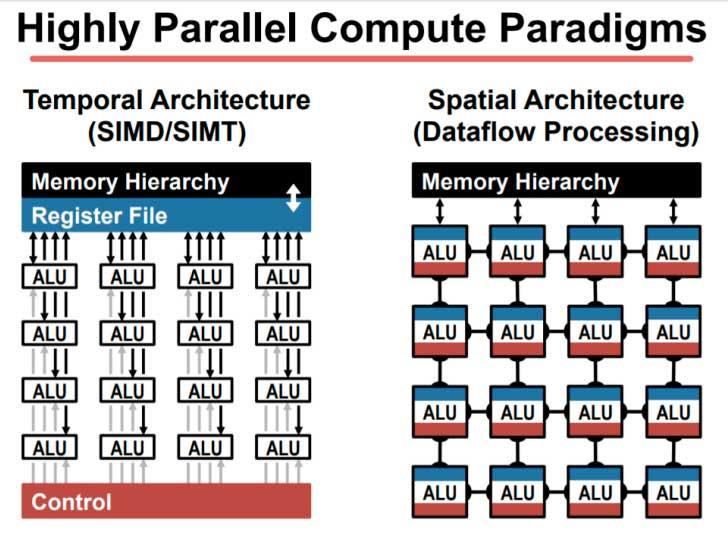

Si hiciéramos una clasificación sobre qué diseños son los más adecuados de cara a los algoritmos de inteligencia artificial la conclusión sería que los que los de tipo MIMD, múltiples instrucciones y múltiples datos, son los que tienen ventaja sobre el resto de arquitecturas.

Dado que las CPU son escalares y por lo general con un poco de SIMD, y las GPU son SIMD en mayor parte y tienen poco de escalar, ha sido necesario la creación de núcleos con ALUs de ejecución MIMD en pos de implementar los algoritmos de inteligencia artificial. Es precisamente en este punto donde entran los FPGA ya que pueden ser configurados para funcionar como múltiples núcleos distintos funcionando en paralelo, y esto ha hecho que muchas implementaciones de IA no se basen en ASICs o chips altamente especializados sino en implementar FPGAs como redes neuronales o arrays sistólicos.

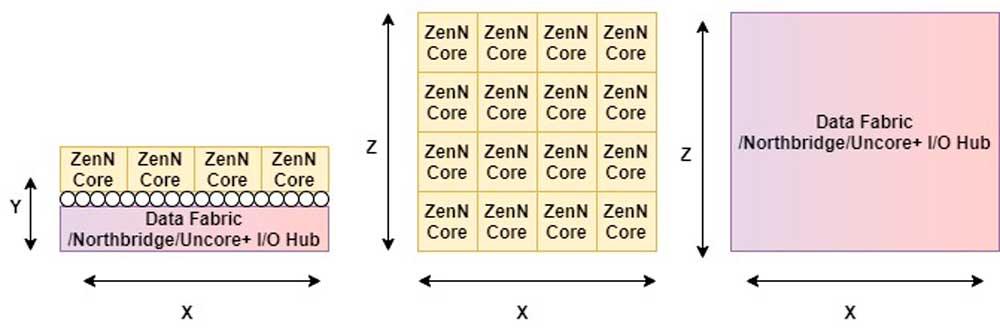

Ese es un mercado al que AMD no puede acceder por el momento debido a que los núcleos en los que se han especializado todo este tiempo no están preparados para cubrir esas necesidades, pero con la adquisición de Xilinx podría tener acceso al mismo y solventar una de las tareas pendientes de AMD de cara a su expansión. Es posible que veamos una nueva familia de procesadores AMD basada en chiplets, pero donde uno o varios de los chiplets sean un FPGA. Esto le va a permitir AMD competir de tú a tú contra Intel en esos mercados, pero el motivo por el cual AMD habría realizado la oferta de compra sobre Xilinx también tiene que ver en cómo estarán diseñados los chips del futuro.

Pero este no sería el único motivo y es que actualmente existe una carencia en AMD que hace que la adquisición de Xilinx sea muy importante para ellos.

El segundo motivo del interés de AMD por Xilinx: El advenimiento de los NoC

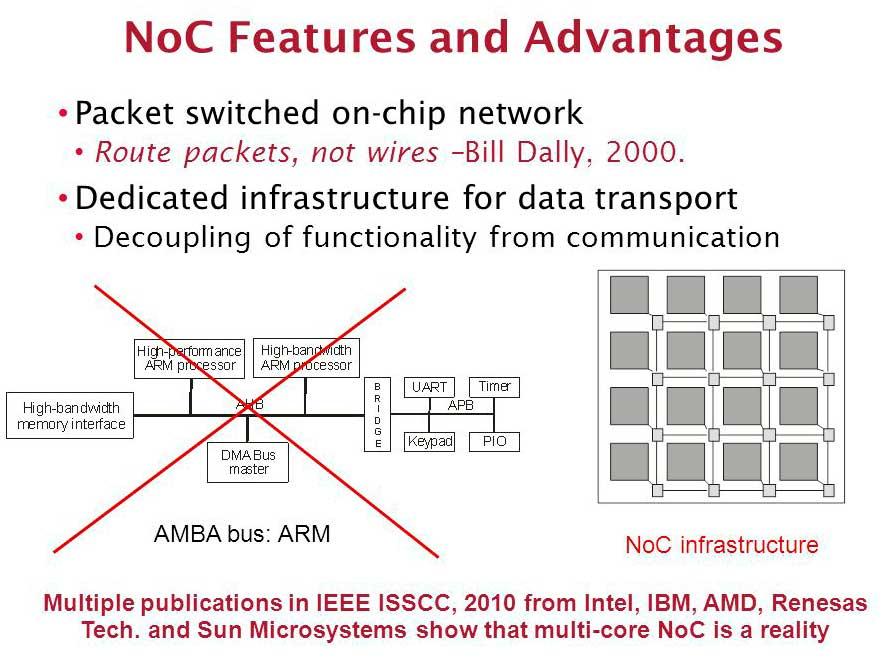

El concepto de NoC es algo que vais a oír y leer mucho en los próximos años. NoC significa red en un chip ya que son las siglas de Network on a Chip. La idea es llevar el concepto de las redes locales a los procesadores y dejar de utilizar matrices de interconexión para comunicar los diferentes elemento dentro de un SoC o un MCM.

La idea es muy simple: a cada elemento independiente de la arquitectura se le coloca un transceptor o router… pensad en que es como si le colocásemos un adaptador de red a cada uno. En vez de tener una matriz central en la que todos los elementos estén interconectados entre si lo que tenemos es que cada elemento del sistema tiene su transceptor, el cual solo ha de «marcar el número» de otro elemento de la infraestructura para comunicarse con él.

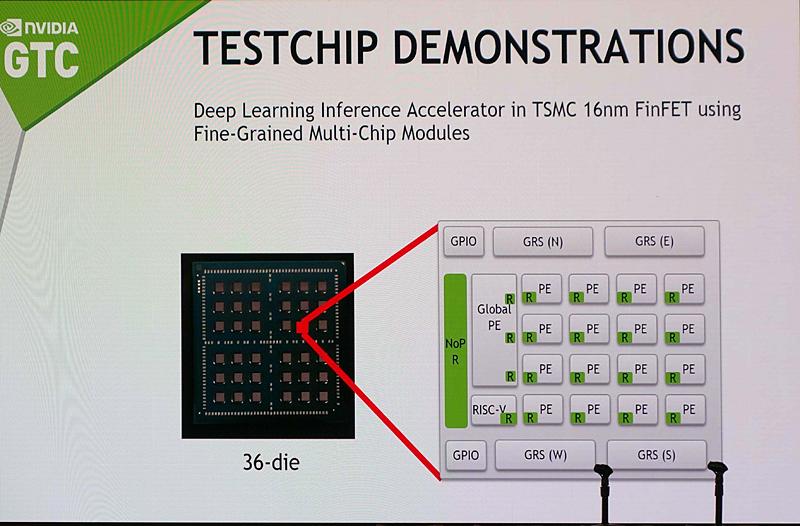

Y esto no es algo que AMD vaya a traer en exclusiva, es una tendencia que todos los diseñadores de procesadores incluyendo Intel y NVIDIA van a integrar. Un ejemplo de NoC nos lo mostró NVIDIA con el chip experimental RC-18.

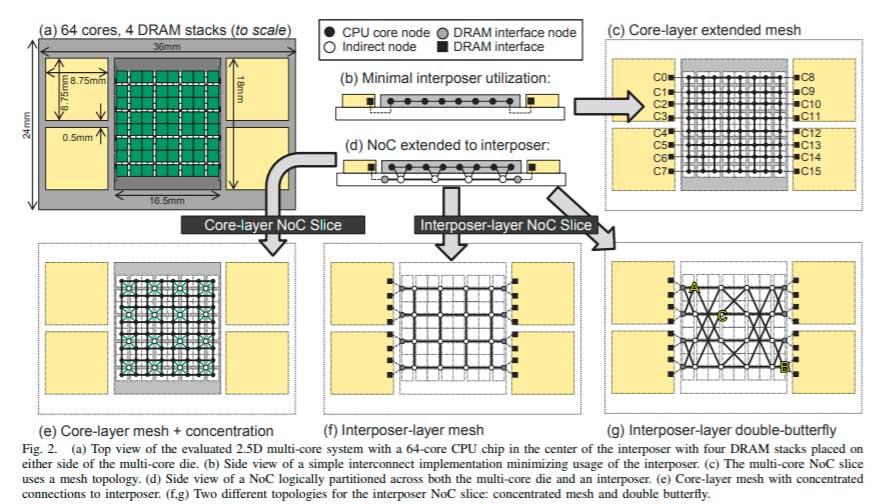

Los GRS en el RC-18 de NVIDIA no son más que transceptores que comunican cada uno de los pequeños chiplets con los chiplets vecinos, pero lo que nos interesa de todo esto es lo que AMD podría implementar y es que existe una potencial configuración 2.5DIC basada en implementar la interfaz de comunicación en el Interposer. Para simplificar las cosas, cada uno de procesadores y aceleradores estarían comunicados a través del Interposer, el cual sería un NoC y estarían conectados al mismo verticalmente.

La parte de las actuales CPUs y SoCs de AMD que se va a mover al Interposer y va a pasar a ser un NoC es el puente norte, conocido como Scalable Data Fabric o SDF, el cual dejará de ser de ser la clásica matriz de interconexión.

Pero en todo esto, ¿dónde entra en juego un FPGA? Pues en toda red necesitamos un controlador de red integrado conocido como NIC, y es en este punto donde la implementación de un FPGA tiene todo el sentido, para poder implementar lo que tradicionalmente se conoce como un SmartNIC.

El «inteligente» controlador de red integrado

El motivo por el cual AMD puede estar interesada en Xilinx es para la implementación de lo que llamamos un SmartNIC, un tipo de unidad que con la llegada de los NoC se está convirtiendo en uno de los elementos más importantes de cara al diseño de nuevas arquitecturas basadas en dicho paradigma.

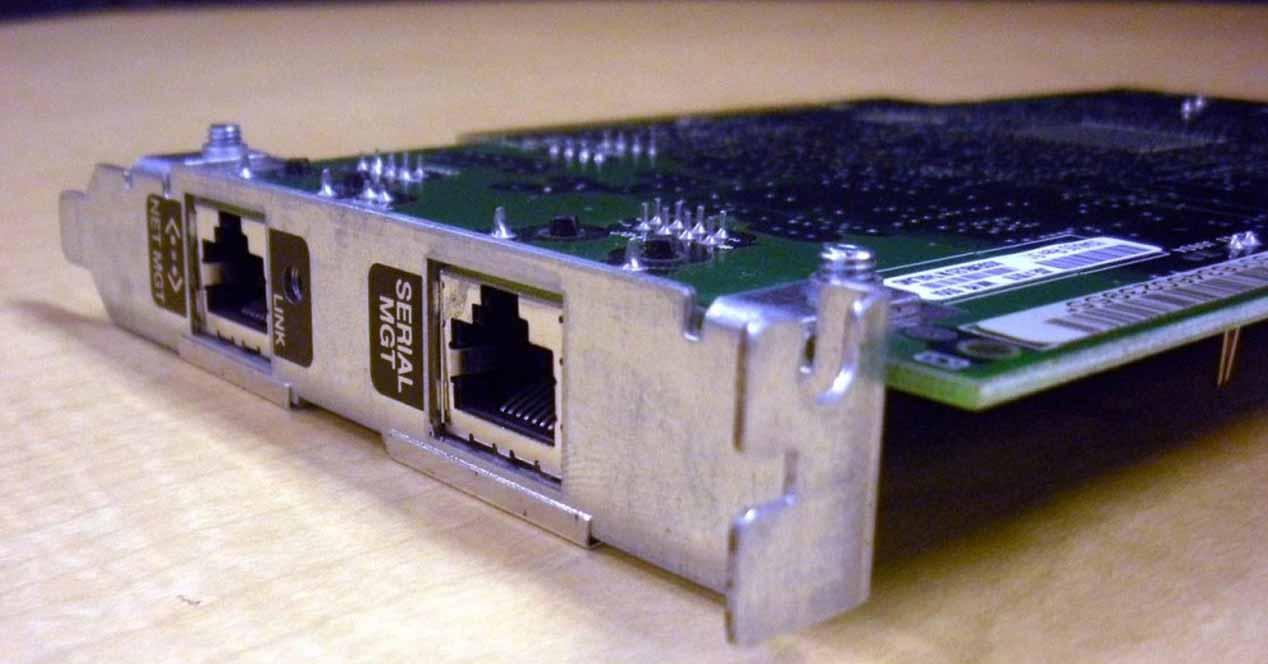

Las tarjetas de red llevan entre nosotros desde el primer PC, reciben el nombre de NIC en inglés ya que son las siglas de “Network Interface Card” y pronto nos daremos cuenta de que los routers que os hemos comentado en la sección anterior son precisamente NICs. ¿Pero acaso no podemos hacerlos un poco más complejos? Al fin y al cabo, que se dediquen solo a enviar paquetes no es del todo eficiente.

La idea sería implementar el SmartNIC en un FPGA, lo que nos permite integrar un controlador de red con extras como por ejemplo un acelerador encargado comprimir y descomprimir al vuelo los datos que se envíen de un procesador a otro, o desde la memoria a un procesador. Pero también podemos integrar un procesador encargado de realizar la gestión de envío de paquetes sin que la CPU central u otro tipo de procesador tenga que tomar parte en el proceso de logística de los datos, por lo que la idea no es otra que la de implementar aceleradores en los routers de cada uno de los elementos que forman parte del NoC.

Es con el advenimiento de los NoC, el interés de la industria en adoptarlos en futuros productos incluyendo a AMD y el porfolio en comunicaciones que tiene Xilinx cuando vemos todo el puzle completo y podemos ver el sentido al interés de AMD por comprar Xilinx, y no solo de cara a implementar aceleradores vía FPGA, sino también de cara al mercado de la inteligencia artificial y para el desarrollo de SmartNICs para los NoC alrededor de los cuales girarán futuros diseños, los cuales en poco tiempo ya no nos parecerán tan futuros.