WD y Toshiba preparan NAND Flash 3D de 128 capas; SSD con un tercio más de capacidad al mismo precio

La NAND Flash está de rigurosa actualidad en este 2019, y es que los precios de los dispositivos que las incluyen están cayendo de precio en mayor o menor medida. Puede que este efecto se vea incrementado ante noticias como la que acaba de ofrecer WD y Toshiba, ya que han terminado el diseño de unas NAND Flash 3D de 128 capas, por lo que la capacidad se aumentará a mismo espacio.

Toshiba NAND Flash 3D BiCS-5: 128 capas con formato TLC

Suena extraño, pero el diseño de este tipo de NAND Flash 3D se basa en el formato de celdas TLC y no QLC.

Esto quiere decir que los dispositivos que las incluyan tendrán 3 bits por celda en vez de cuatro como se esperaba en un principio.

La ventaja es que en vez de incluir las 96 capas que están en plena producción actualmente como novedad en estos momentos, tendremos 128 capas, pero ¿qué significa esto?

Pues es sencillo, hay dos maneras de aumentar actualmente la capacidad de los SSD y RAM (entre otros): aumentar los bits por celda o aumentar las capas a cada mm2 de superficie.

Al pasar de 96 capas a 128 capas WD y Toshiba obtendrían un tercio más de capacidad, asumiendo claro que utilizaran la misma tecnología que en el proceso anterior.

También cabe la posibilidad de obtener la misma capacidad a un costo menor, reduciendo el precio de los dispositivos que la incluyesen de manera abrupta.

¿Qué empresa tiene la mayor densidad NAND de la industria?

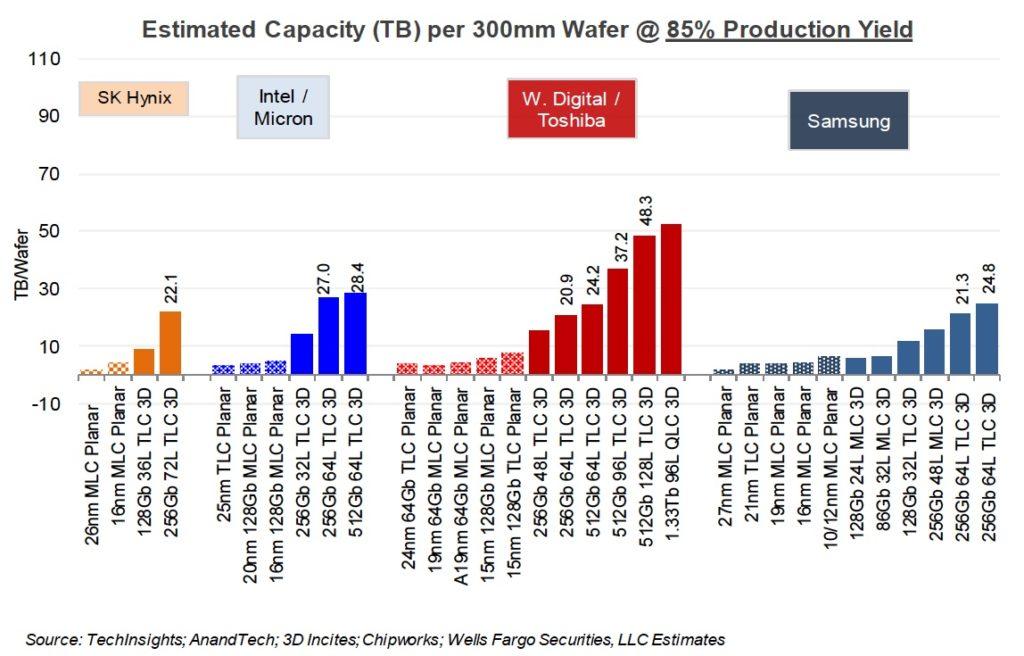

Cuatro grandes fabricantes se reparten la mayor parte del pastel de la NAND Flash 3D actualmente: SK Hynix, Intel/Micron (ya legalmente separadas), WD/Toshiba y finalmente Samsung.

Según el analista senior de Wells Fargo, Aaron Rakers, si seleccionamos las obleas más típicas del mercado (300 mm) la capacidad de TB por mm2 es bastante variada entre los 4 grupos, tal y como muestra el siguiente gráfico.

Como se ve, WD y Toshiba lideran con solvencia la densidad de obleas por GB y mm2. Esto ha sido posible por el tipo de matriz que han usado, ya que su diseño se basa en CuA (Circuito bajo Array o Circuit-under-array).

Este diseño permite que los circuitos lógicos se construyan en la parte inferior del chip, apilando las capas en la parte superior, lo cual consigue un tamaño de matriz un 15% más pequeño si lo comparamos con tecnologías no CuA.

La nueva tecnología de NAND Flash 3D de 128 capas amplía todavía más las cifras, ya que el tamaño de la matriz se reduciría un 23% si lo comparamos con la tecnología actual de 96 capas.

Mayor espacio es igual a mayor rendimiento

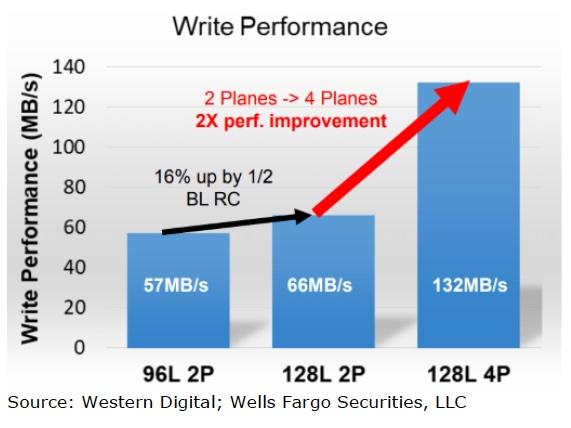

El diseño de las NAND Flash es complejo, y por ello detalles como el mayor espacio para matrices y planos es sinónimo de un mayor rendimiento por norma general.

WD y Toshiba han conseguido con su diseño CuA que cada reducción de tamaño proporcione un aumento de rendimiento. Si efectivamente consiguen reducir un 23% el espacio de la matriz a utilizar significaría que podrían utilizar un aumento de planos (Planes) para mejorar su performance.

Así, el salto sería del doble de rendimiento al pasar de 2 Planes a cuatro, todo a mismo número de capas usadas.

Esto es debido a que cada Plane es un plano o sección independiente que puede ser accedido de forma independiente y en paralelo, por lo tanto, el rendimiento es multiplicado por el número de planes que se añaden, siendo 100% escalable.

Así, cada dispositivo pasaría a disponer de por cada 128 capas de unos 132 MB/s de rendimiento bruto, frente a los 66 MB/s que se conseguirían con 2 Planes.

A modo comparativo, los chips Samsung contienen 110 capas y consiguen 83 MB/s actualmente, siendo de las más rápidas de la industria, lo cual evidencia el salto que Western Digital y Toshiba planean dar al mercado.