¿Cómo se consiguen reducir los nanómetros de un procesador, y por qué es tan difícil?

Todos sabemos que los fabricantes están siempre ansiosos por reducir el proceso de fabricación de sus componente a un nuevo nodo, que les permita reducir los nanómetros de los transistores que hay en su interior. Pero ¿por qué este afán en reducir su tamaño? Y ¿cómo consiguen llevar a cabo esta reducción de una manera satisfactoria?

La reducción de los nodos de fabricación de los componentes electrónicos es siempre uno de los principales objetivos de los diseñadores de chips, ya sean estos para memoria, para procesadores, núcleos gráficos, etc. Un nodo de fabricación más bajo que el que se use en cualquier momento para fabricar un componente, presenta muchas ventajas para el diseñador / comerciante del chip:

- Con un nodo más pequeño y mismo número de transistores, se pueden obtener mayor número de chips por cada oblea de silicio, con lo que sale más barata su fabricación.

- Por el contrario, podríamos emplear todo el espacio libre que deja el nuevo nodo de fabricación para meter todavía más transistores dentro del componente. Esto, habitualmente, suele traducirse en un incremento del rendimiento.

- La reducción del nodo trae consigo una reducción de la energía que es necesaria para que los transistores cambien de estado. Por tanto, el componente, si no se le incorporan más transistores, consumirá menos.

- Otra opción es mantener el mismo techo de consumo de potencia, añadiendo más transistores al núcleo.

Una muestra muy clara de lo que es la reducción en nanómetros del nod0 de fabricación es lo que ha hecho AMD con sus procesadores Ryzen. Los de 1ª Generación estaban fabricados en un nodo de 14 nm. Cuando AMD bajó su nodo a los 12 nm, empleó la reducción para implementar algunas mejoras, pero manteniendo, prácticamente, la misma envolvente térmica. El hecho es que, gracias a esta reducción del nodo, los nuevo Ryzen de 2ª Generación tienen una mayor frecuencia de funcionamiento, con un TDP que se ha mantenido igual (más o menos, y excepto en el caso de los Ryzen 7 2700X).

Reducir los nanómetros de los nodos de fabricación nos obliga a lidiar con la Ley de Moore

Sin embargo, reducir el nodo de fabricación trae consigo una serie de problemas asociados con los que han de lidiar las fábricas que producen los componentes:

- Las vías de datos / corriente se van haciendo tan pequeñas, a medida que se reducen los nanómetros de los nodos, que es muy complejo mantener su integridad, y se deterioran con facilidad, algo que es creado por el fenómeno de la electromigración. Ello da paso al problema de los electrones metiéndose en las vías donde no deben de ir.

- Es más complejo hacer las trazas de datos entre los transistores.

- Los transistores se vuelven mucho más sensibles a los cambios de voltaje. Lo cual es positivo, sí, pero también negativo.

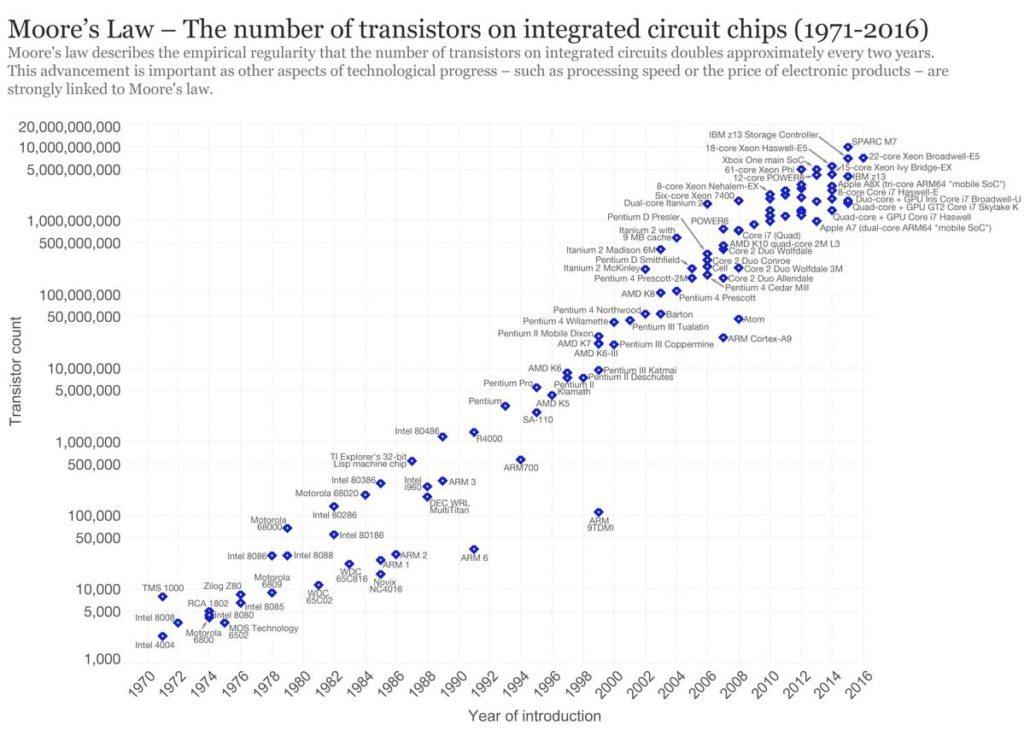

Suponemos que todos habéis oído hablar de la Ley de Moore. Esta Ley, formulada por Gordon Moore, uno de los cofundadores de Intel, afirma que «cada dos años se reduce el nodo de fabricación a la mitad, con lo que se dobla en número transistores que se puede meter en cada chip». Esta Ley es el principal causante del periodo de alternancia «tick – tock» que ha tenido Intel durante décadas en la fabricación de sus procesadores.

El problema es que la Ley de Moore no preveía que los problemas que se encontraría Intel al reducir sus nodos de fabricación harían que esta se quedara estancada en el nodo de 14 nm desde hace ya algunos años, dado que por algún motivo que desconocemos, el nodo de 10 nm se le está resistiendo bastante al gigante azul. Por contra, tanto Samsung como TSMC ya han comenzado la fabricación de componentes en el nodo de 7 nm y ya se está hablando, incluso, de producir a 3 nm.

¿Cómo se reducen los nanómetros en los nuevos nodos de fabricación?

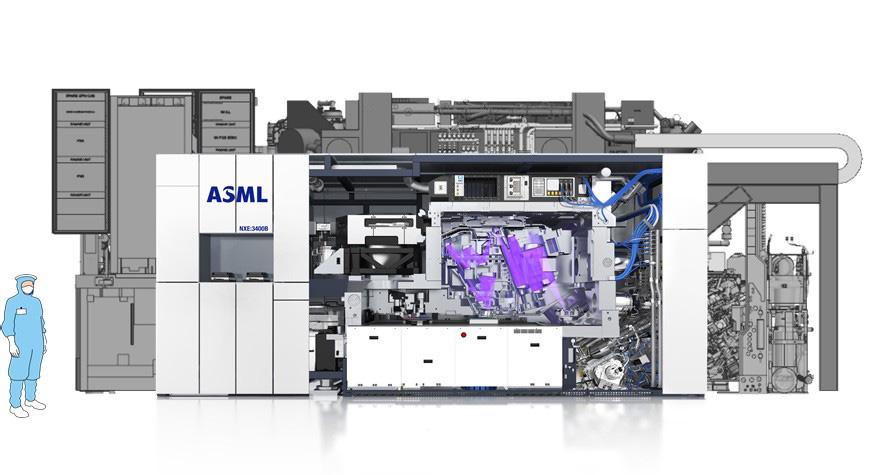

Para reducir el proceso de fabricación se emplean, a parte del consabido proceso de revisión de todos los diagramas lógicos del componente, máquinas de litografía de diferentes métodos, entre ellos la luz ultravioleta.

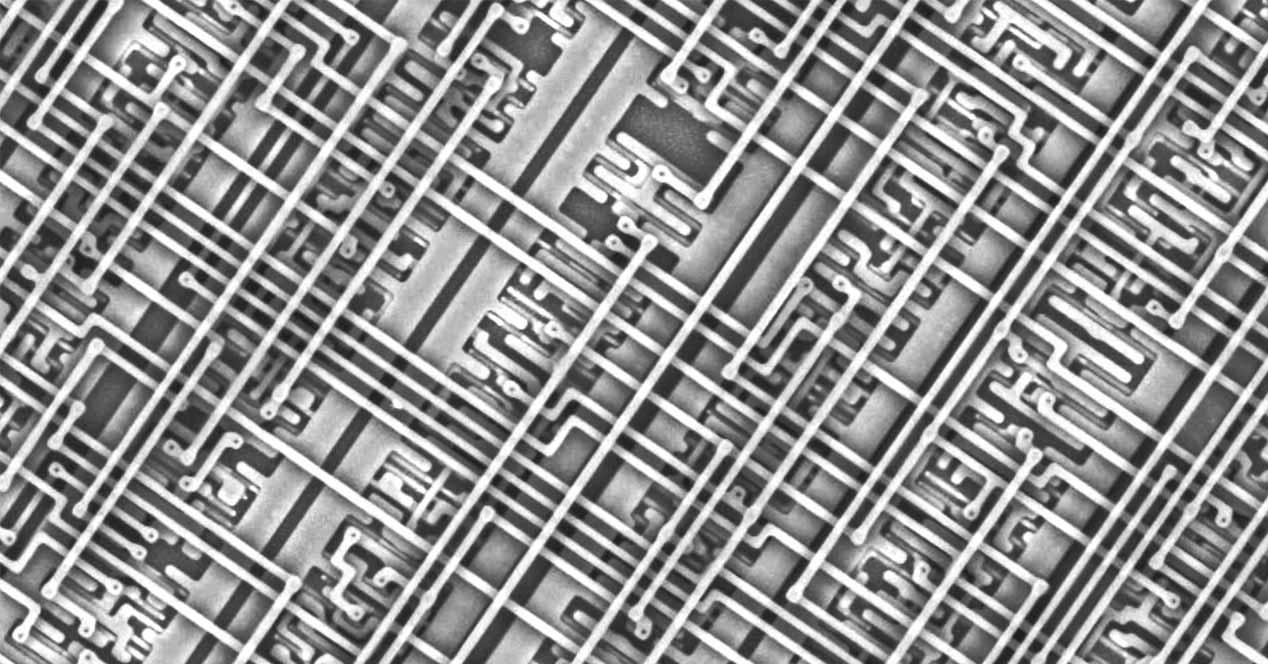

El proceso comienza creando una máscara fotográfica que se emplea como plantilla maestra para una de las capas del componente (sí, los componentes llevan años haciéndose en tres dimensiones). Esta plantilla se instala en una máquina de litografía, donde se proyecta luz a través de la máscara, que se imprime en la oblea de silicio, creando tanto los transistores como sus correspondientes vías de datos. Una vez se ha creado la primera capa, se produce la siguiente y así, de manera sucesiva.

Actualmente, las máquinas de litografía más avanzadas que hay son las EUV o Extreme Ultra Violet de ASML. Pero, para que os hagáis una idea de lo que es una de estas máquinas, su tamaño es gigantesco (al igual que su precio, que se cifra en varios millones de dólares). Son tan grandes y complejas que han de construirse directamente en la fábrica que las va a usar, y se suele tardar una media de 30 días en completar la construcción y calibración de una de ellas.