Un ingeniero de desarrollo de AMD ha permitido que se filtren jugosos detalles de cómo será el funcionamiento interno del nuevo procesador Zen de AMD al subir un parche para un proyecto para Linux entre cuyas líneas de código se podía entrever cómo debía manejar ese sistema operativo el nuevo procesador. Este «pequeño» desliz nos permite empezar a hacernos una idea de cómo funionará el procesador y qué mejorías podremos esperar de él cuando se lance al mercado.

La actual arquitectura de los procesadores de escritorio de la gama FX nunca llegó a tener un gran calado entre los usuarios dado un rendimiento que lo dejaba generalmente por detrás de sus contapartes de Intel. Esta falta de rendimiento ha sido atribuida a una pipeline excesivamente larga, a una mala implementación de la rama de predicción y a que el software no se desarrolló tal y como AMD pretendía que se hiciera, dado que en aplicaciones muy paralelizables los procesadores no rinden nada mal.

El trabajo de un ingeniero de AMD en el código de Linux ha permitido comenzar a ver ciertos detalles de la arquitectura interna del que va a ser su nuevo procesador, denominado Zen. En las líneas de código podemos ver cambios notables en la arquitectura frente a la actual Piledriver y que presagian grandes cosas para el nuevo procesador.

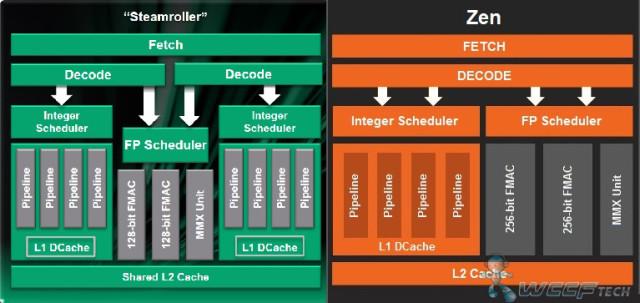

Lo primero es que el número de unidades lógicas de aritmética (ALUs) permanece en 4 en el nuevo procesador pero, a diferencia frente a Piledriver, cada núcleo es un núcleo completo en el que se integran dos unidades de generación de direcciones (AGUs) y, aunque el programador del integrador se reduce a tan solo 1 unidad, cada núcleo tiene una unidad de coma flotante para si mismo en lugar de tener que compartirla con otro núcleo como sucede actualmente. En realidad, esta aproximación es bastante similar a cómo AMD desarrolló en el pasado sus exitosos Phenom II.

Este descubrimiento cada vez hace más creíbles los comentarios de AMD en su Analyst Day sobre un incremento de un 40% en el rendimiento de instrucciones por ciclo de reloj (IPC). Esto también se ve reforzado por la implementación de puntos de control en la pipeline que permiten comprobar si una instrucción se está desarrollando correctamente y dehecharla más pronto encaso de no ser así, algo similar a lo que tenían los Sandy Bridge de Intel los cuales, a pesar de tener una pipeline tan grande como los procesadores de AMD, eran mucho más eficientes procesando instrucciones en ella.

Este descubrimiento cada vez hace más creíbles los comentarios de AMD en su Analyst Day sobre un incremento de un 40% en el rendimiento de instrucciones por ciclo de reloj (IPC). Esto también se ve reforzado por la implementación de puntos de control en la pipeline que permiten comprobar si una instrucción se está desarrollando correctamente y dehecharla más pronto encaso de no ser así, algo similar a lo que tenían los Sandy Bridge de Intel los cuales, a pesar de tener una pipeline tan grande como los procesadores de AMD, eran mucho más eficientes procesando instrucciones en ella.

Parece ser que las cosas pintan bastante bien para este nuevo procesador. Personalmente yo lo estoy esperando con bastantes ganas.